Negative capacitance molybdenum disulfide transistor based on ferroelectric gate dielectric and preparation method thereof

A ferroelectric gate dielectric, molybdenum sulfide technology, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve problems such as heat generation that cannot be ignored, limit chip operating speed, and lower operating frequency upper limit, etc. Circuit integration, avoiding slow device turn-on and fast turn-on effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

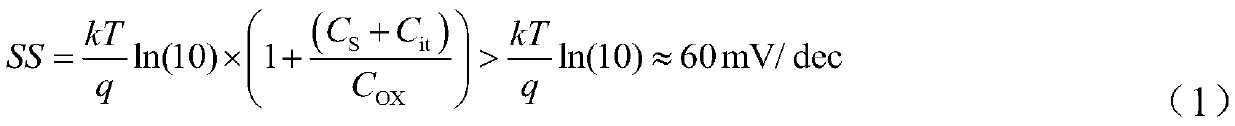

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0029] This embodiment provides a method for preparing a negative capacitance molybdenum disulfide transistor based on a ferroelectric gate dielectric. The preparation method includes, first, SiO 2 Substrates are cleaned, SiO 2 The specific cleaning process of the substrate is as follows:

[0030] 1) Ultrasonic cleaning with acetone, the ultrasonic frequency is 45-50KHz;

[0031] 2) Ethanol ultrasonic cleaning, the ultrasonic frequency is 50-55KHz;

[0032] 3) Rinse in a beaker of deionized water;

[0033] 4) Boil in concentrated sulfuric acid: hydrogen peroxide = 4:1 (volume ratio) mixture at 90°C for 15 minutes, rinse with deionized water. The concentration of sulfuric acid is 98%, and the concentration of hydrogen peroxide is 40%.

[0034] Put the cleaned material into the CVD equipment to grow molybdenum sulfide material. The CVD met...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| band gap | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com