Wafer-level heterogeneous integrated high-frequency system and manufacturing method thereof

A wafer-level, heterogeneous technology, applied in the field of microelectronics, can solve the problems of serious bonding loss and parasitic effects, unfavorable development of system miniaturization, and reduced overall system performance, so as to reduce the influence of parasitic effects and shorten the internal The effect of interconnection and risk reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] The present invention will be described in further detail below with reference to specific embodiments, but the embodiments of the present invention are not limited thereto.

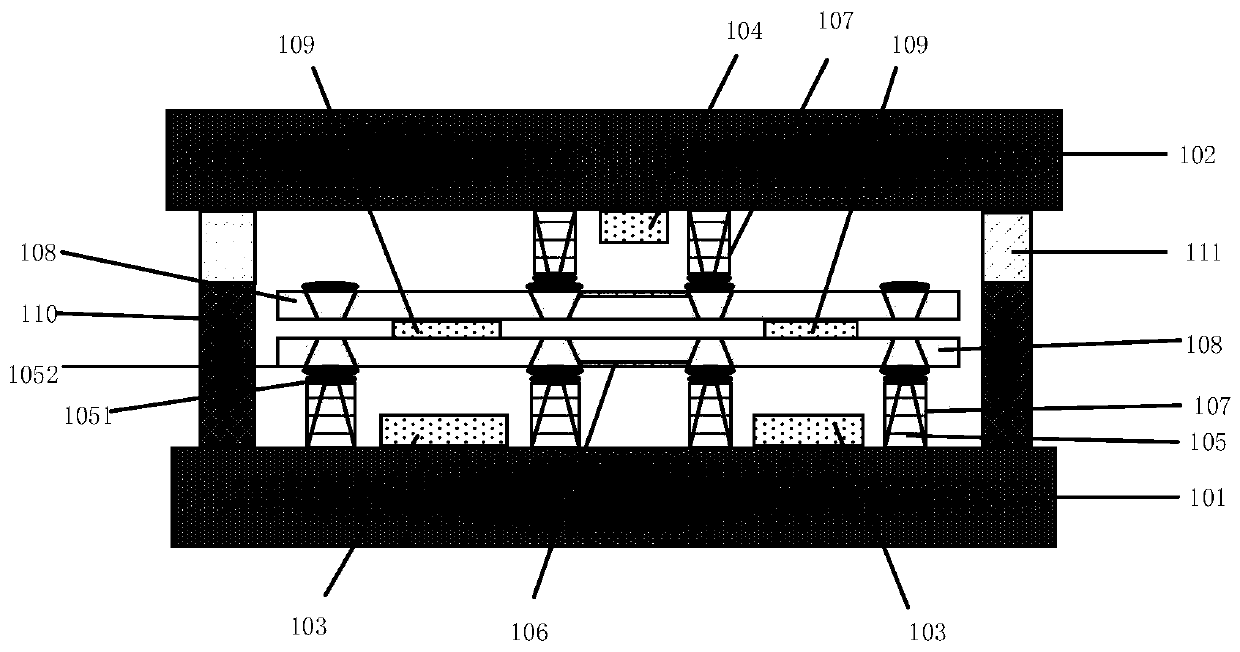

[0040] The invention provides a wafer-level heterogeneous integrated high-frequency system, the structure is as follows figure 1 As shown, it includes at least a first substrate 101, a second substrate 102, an insulating bonding layer, and at least two chips arranged in different layers; wherein:

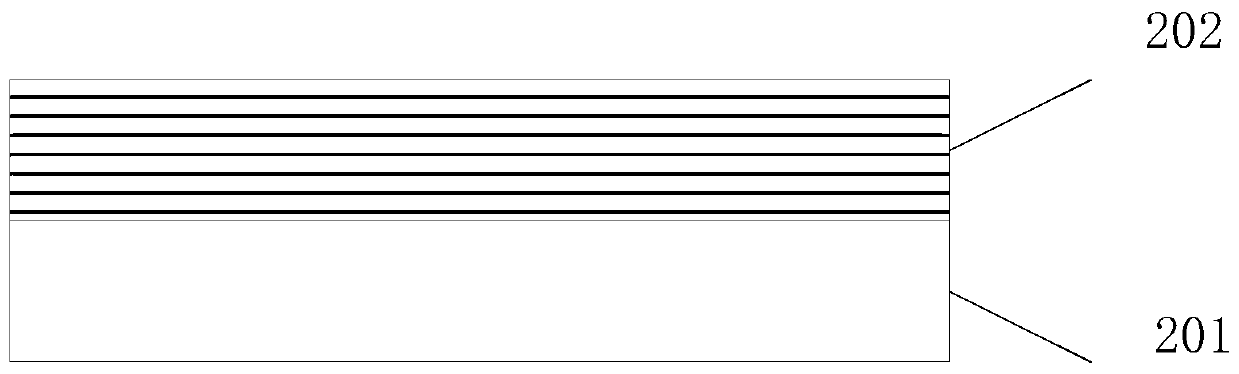

[0041] The second substrate 102, the insulating bonding layer, and at least two chips are disposed between the first substrate 101 and the second substrate 102, including a first chip 103 connected to the first substrate 101, and a first chip 103 connected to the first substrate 101. the second chip 104 connected to the second substrate 102;

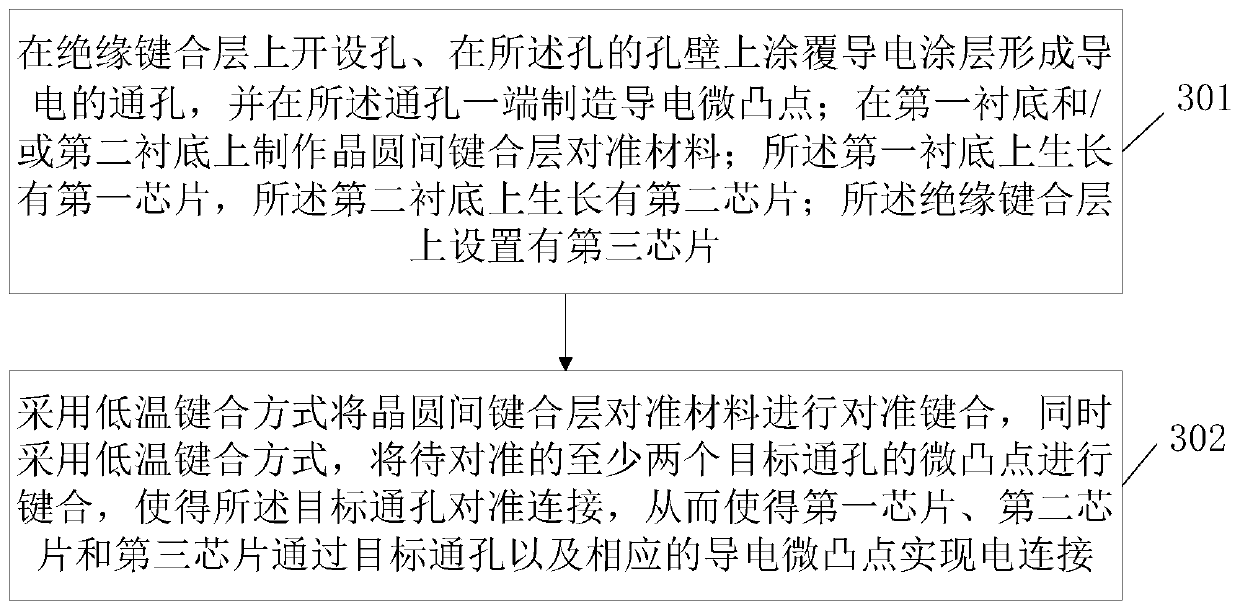

[0042] At least one through hole 105 is provided on the insulating bonding layer, and the side wall of the through hole 105 is coated with a conductive coating; ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More