A near-room temperature preparation process of high performance thin film transistor and application

A thin-film transistor and fabrication process technology, applied in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve problems such as the inability to prepare fully transparent devices, the difficulty of precise control of film thickness, and the inability to be compatible with flexible plastic substrates. , to achieve the effect of good optical response characteristics, excellent electrical characteristics, and precise and controllable thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

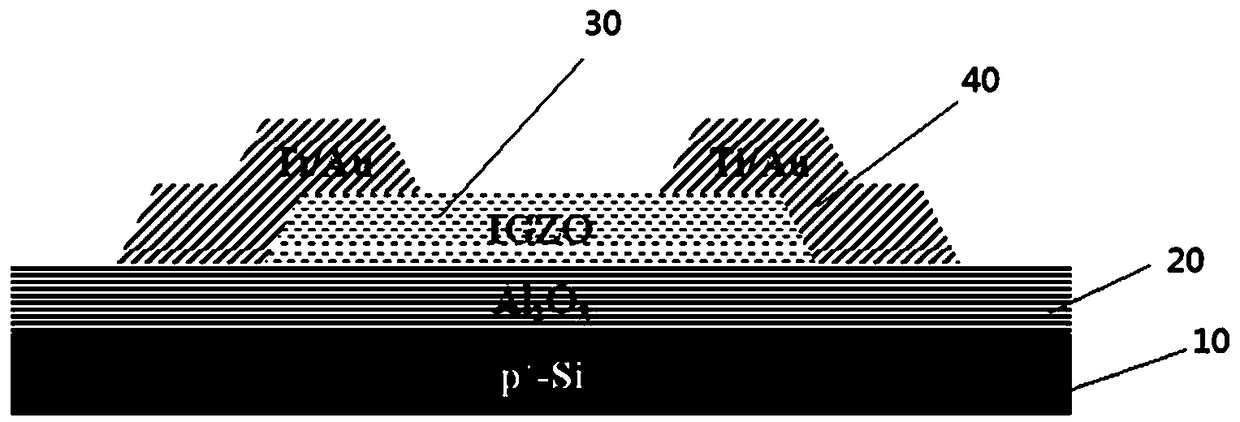

[0028] Put the heavily doped P-type Si substrate 10 into the ALD reaction chamber, and deposit Al at 30°C 2 o 3 Gate insulating layer 20, its thickness is 40nm; Will grow Al 2 o 3 The Si substrate of the gate insulating layer is placed in the magnetron sputtering deposition chamber, and the IGZO layer 30 is grown at near room temperature with a thickness of 40nm. Then the obtained device is processed in a clean room. Firstly, the first photolithography is carried out to make the photoresist form a channel pattern on the surface of the film, and then a dilute hydrochloric acid solution is arranged to etch the IGZO film to form a channel, and then acetone is used to remove residual photoresist on the surface. Then the second photolithography was carried out, and the negative gel was uniformly coated on the surface of the sample, and then exposed under the exposure machine for 30 seconds, and then developed with a negative gel developer to form a source-drain electrode pattern...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More