Transistor with embedded source and drain and preparation method of transistor

A transistor and embedded technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of reducing the effective drive current of the device, the influence of overlay errors, and reducing the integration density, achieving small device size, high Pressure resistance, small size effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

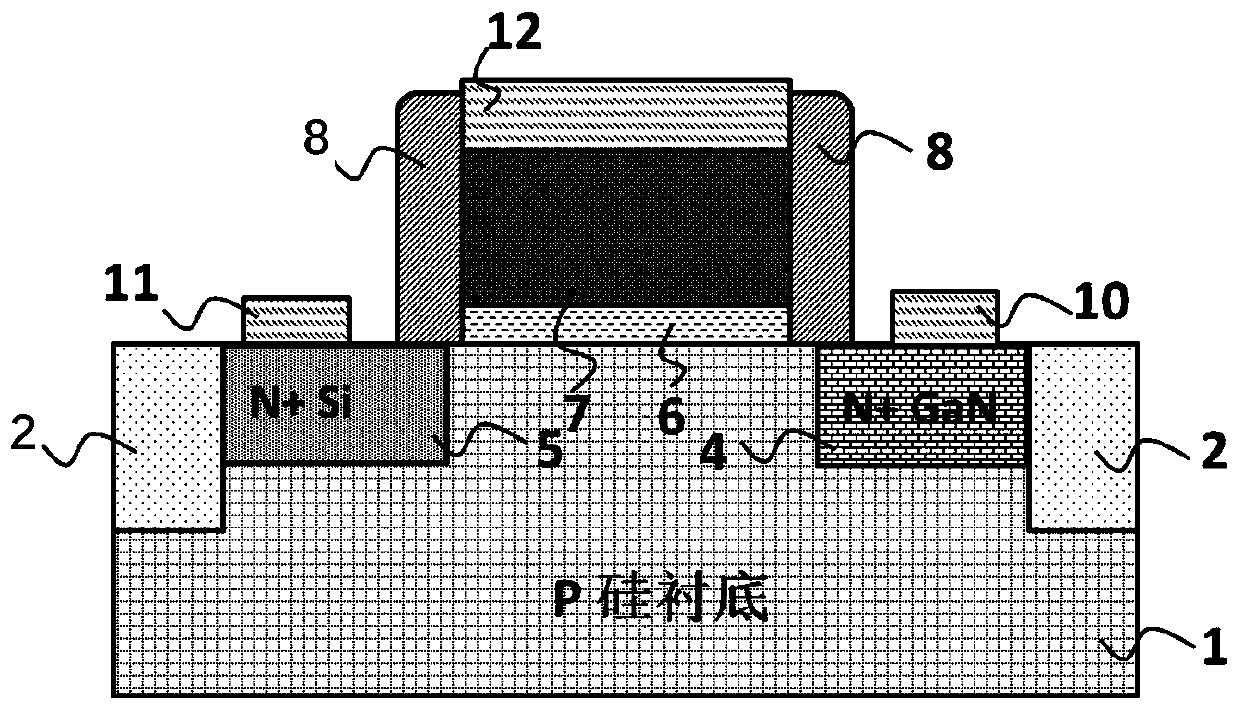

[0041] Embodiment 1 This embodiment provides a high withstand voltage field effect transistor with embedded source and drain

[0042] Such as figure 1Shown is a schematic diagram of the transistor structure, including a weakly p-type doped silicon substrate 1; trench isolation regions 2 embedded in both ends of the silicon substrate 1, and the upper surface of the trench isolation region 2 is in contact with the silicon substrate The upper surface of the bottom 1 is coplanar; the heavily N-type doped drain 4 and the heavily N-type doped source 5 embedded near both ends of the silicon substrate 1; the heavily N-type doped drain 4 The heavily N-type doped source 5 is in contact with the trench isolation region 2, and the heavily N-type doped drain 4 and the heavily N-type doped source 5 top surfaces are in contact with the silicon substrate 1 top surface Coplanar; the gate oxide layer 6 on the silicon substrate 1; the gate 7 on the gate oxide 6; the gate contact 12 on the gate ...

Embodiment 2

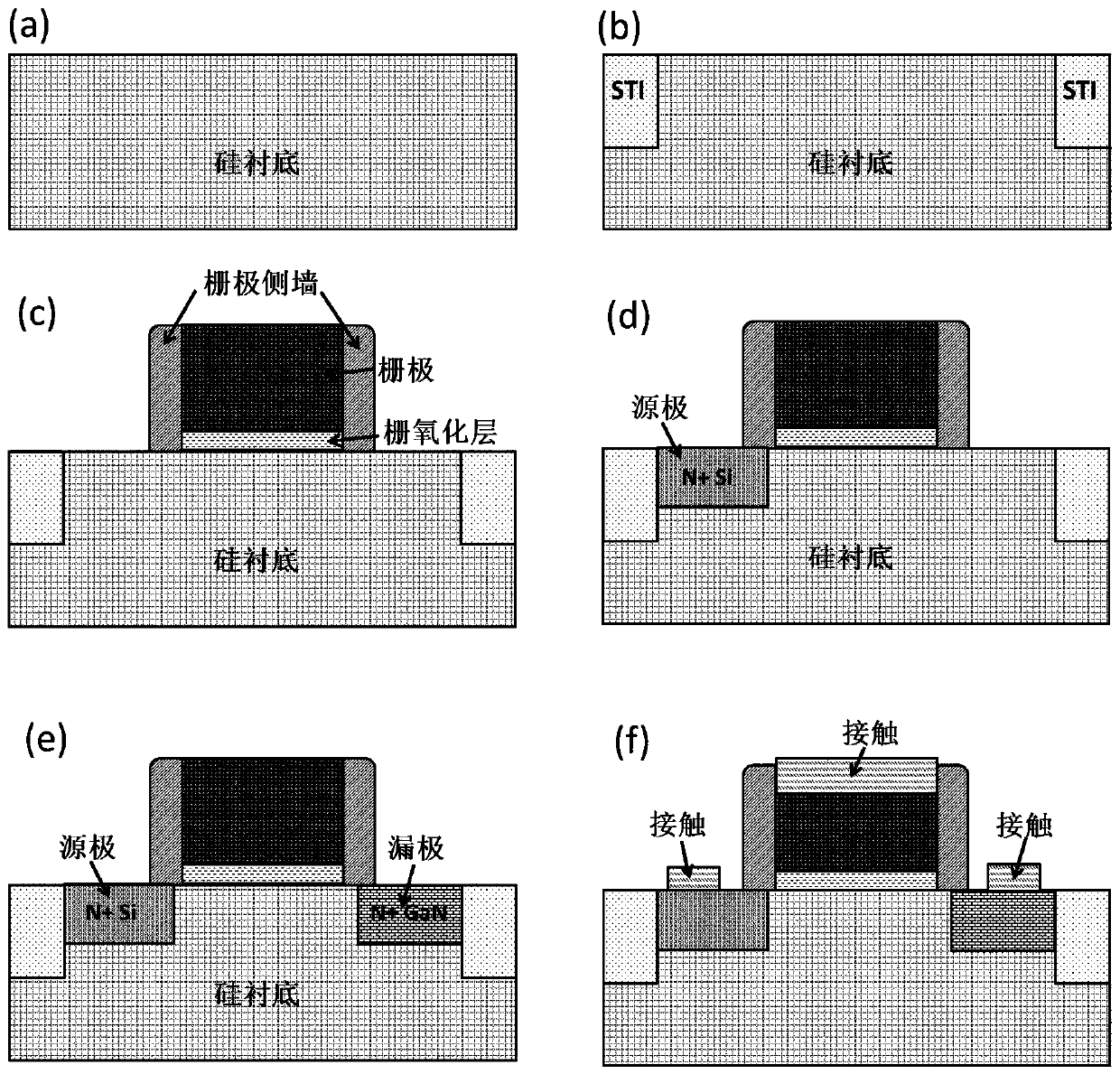

[0053] Embodiment 2 This embodiment provides a novel method for manufacturing a high withstand voltage field effect transistor with embedded source and drain

[0054] Such as image 3 (a) The schematic structure of the transistor shown in (a), the initial bulk silicon substrate is selected, and the substrate is doped with weak p-type doping, and the doping concentration is 10 17 cm -2 , the substrate is a silicon-based material deposited on an insulating layer.

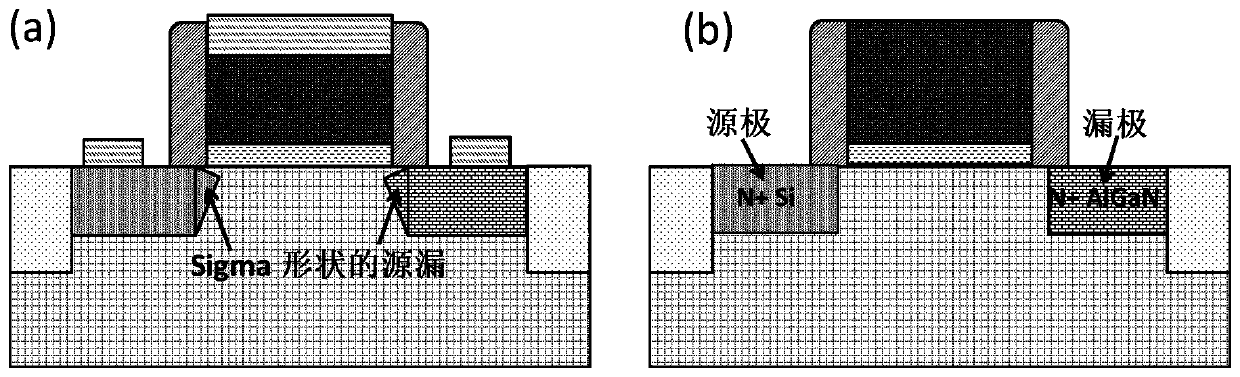

[0055] Chemical vapor deposition of a layer of aluminum oxide gate oxide layer with a thickness of 10nm and a layer of polysilicon positive gate with a thickness of 100nm; photolithography and open the window of the positive gate pattern, and then use photoresist as a mask to align the positive gate The gate is dry etched to form a pattern of the gate, and KOH solution is used for wet etching.

[0056] Atomic layer deposition of a layer of low dielectric constant dielectric SiOCN as the gate spacer material, follow...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More