GaN-based normally-off high-electron-mobility transistor and preparation method thereof

A high electron mobility, normally-off technology, applied in transistors, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as device performance impact, etching process damage, and threshold voltage not high enough to achieve good high-frequency performance, The effect of low on-resistance and high threshold voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

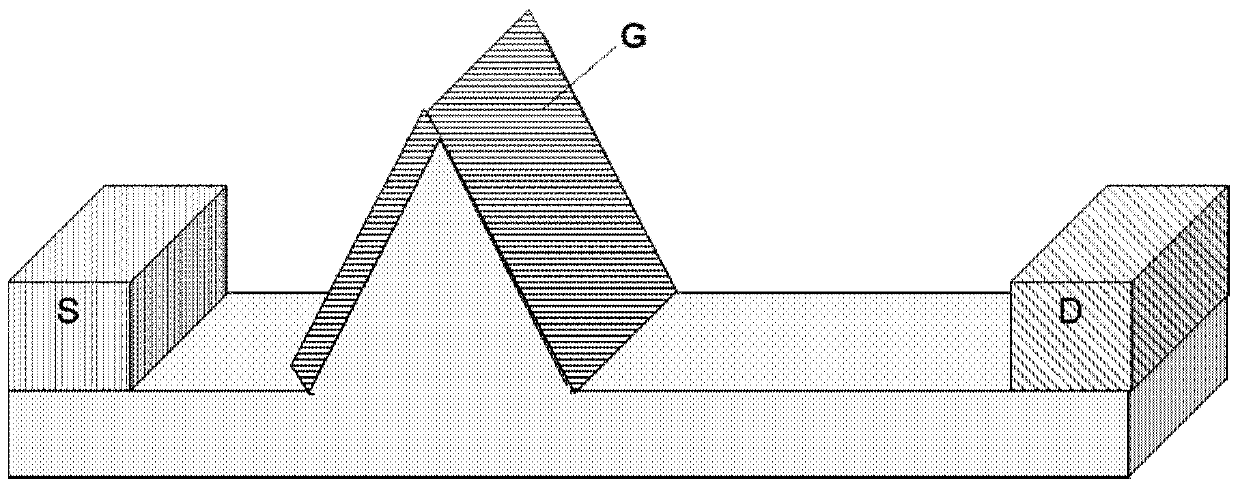

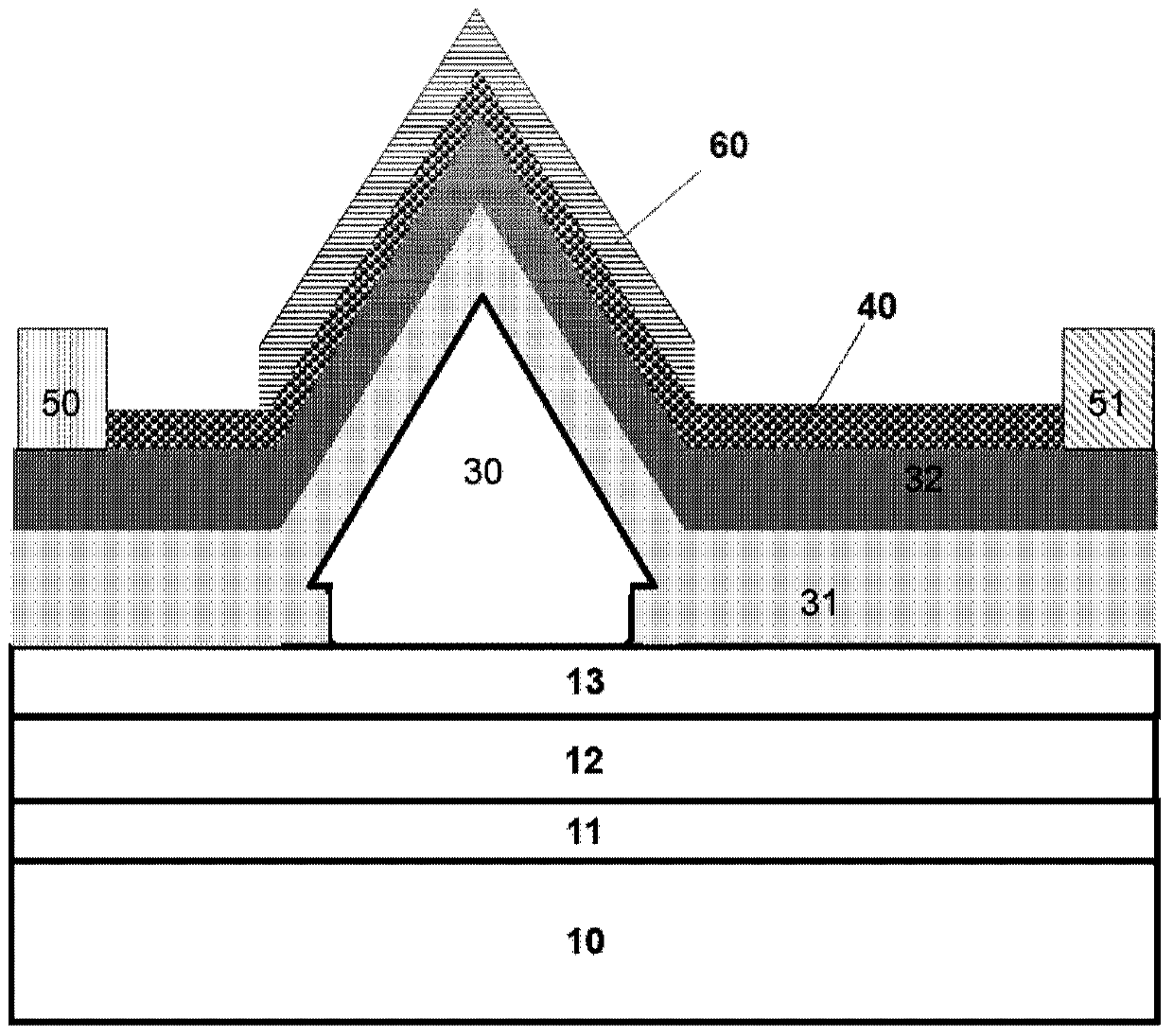

[0039] figure 1 Schematically showing a top view of a GaN-based normally-off high electron mobility transistor structure with a triangular prism slope channel provided by an embodiment of the present invention, figure 2 Schematically showing a cross-sectional view of a GaN-based normally-off high electron mobility transistor structure with a triangular prism slope channel provided by an embodiment of the present invention, as shown in figure 1 and figure 2 As shown, the GaN-based normally-off high electron mobility transistor of the triangular column slant channel may include, for example:

[0040]Substrate 10, a nucleation layer 11, a buffer layer 12, a first high-resistance GaN layer 13, a ridge-shaped GaN layer 30, a ridge-shaped channel layer 31, and a ridge barrier are sequentially formed on the surface of the substrate 10 from bottom to top. layer 32 and the ridge-shaped dielectric layer 40 , the source electrode 50 and the drain electrode 51 are prepared on the ridg...

Embodiment 2

[0052] Figure 4 Schematically showing the top view of the GaN-based normally-off high electron mobility transistor structure of the trapezoidal column slope channel provided by the embodiment of the present invention, Figure 5 A cross-sectional view schematically showing a GaN-based normally-off high electron mobility transistor structure with a trapezoidal column slope channel provided by an embodiment of the present invention, as shown in Figure 4 and Figure 5 As shown, compared with the GaN-based normally-off high electron mobility transistor of the above-mentioned triangular prism slope channel, the difference is that the structure of the slope channel is a trapezoidal column, and other structural details are the same as those of the GaN-based normal transistor of the above-mentioned triangular prism slope channel The same is true for off-type high electron mobility crystals, and will not be repeated here.

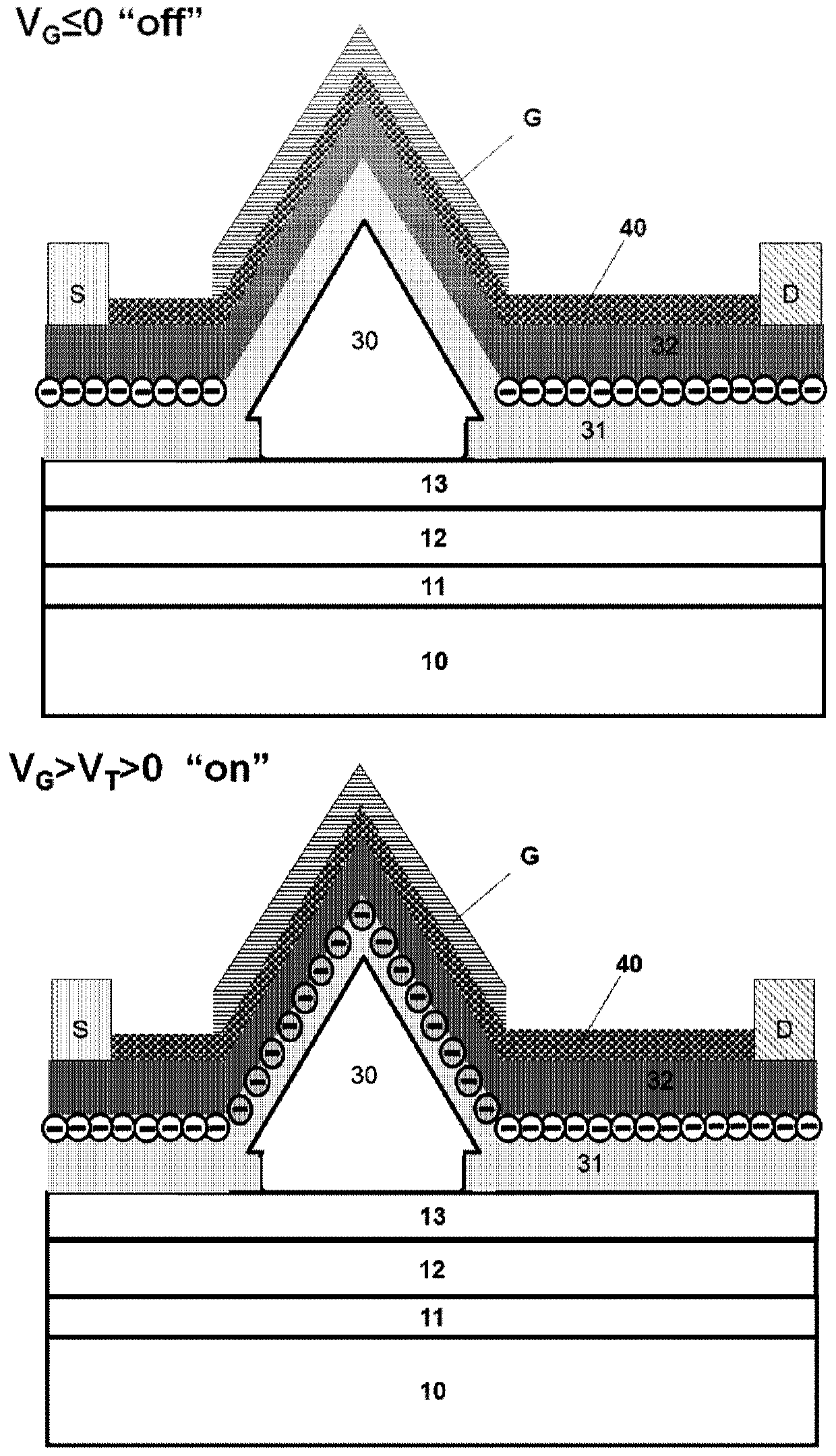

[0053] Image 6 Schematically showing the working principl...

Embodiment 3

[0056] Figure 7 Schematically shows a flow chart of a method for preparing a GaN-based normally-off high electron mobility transistor with a triangular or trapezoidal slanted channel provided by an embodiment of the present invention, as shown in Figure 7 As shown, the method may, for example, include operations S1-S5.

[0057] S1 , sequentially preparing a nucleation layer 11 , a buffer layer 12 and a first high resistance GaN layer 13 on the substrate 10 .

[0058] In a feasible manner of this embodiment, the nucleation layer 11, the buffer layer 12 and the first high-resistance GaN can be sequentially grown on the substrate 10 by Metal-organic Chemical Vapor Deposition (MOCVD). Layer 13, forming a GaN template, has a structure such as Figure 8 middle a or Figure 9 Shown in a. Wherein, the growth temperature of the nucleation layer 11 may be, for example, 500-1000°C.

[0059] S2 , preparing a patterned dielectric layer 20 on the first high resistance GaN layer 13 . ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More