Passivation contact solar cell and preparation method thereof

A technology for solar cells and passivation layers, applied in the field of solar cells, can solve problems such as process limitations and inability to make a suede surface, and achieve the effects of reducing the recombination rate, improving the light utilization rate, and the method is simple

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0045] A kind of preparation method of passivated contact solar cell provided by the invention comprises the following steps:

[0046] (1), preparing a tunneling oxide layer on the back surface of the N-type crystalline silicon substrate, and preparing a phosphorus-doped polysilicon layer on the tunneling oxide layer;

[0047] (2), preparing silicon nitride anti-reflection layer on the phosphorus-doped polysilicon layer on the back surface of the N-type crystalline silicon substrate; the silicon nitride anti-reflection layer is also used as a mask on the back surface of the N-type crystalline silicon substrate;

[0048] (3), put the N-type crystalline silicon substrate into the alkaline solution, and carry out alkali-texturing treatment on the front surface of the N-type crystalline silicon substrate. During the treatment, the silicon nitride mask on the back surface of the N-type crystalline silicon substrate is Thin;

Embodiment 1

[0069] (1) Take an N-type crystalline silicon substrate 1 with a resistivity of 1Ω·cm and a thickness of 170 μm, and place the N-type crystalline silicon substrate 1 with a resistivity of 1Ω·cm and a thickness of 170 μm in a 20wt% NaOH solution , at a temperature of 85° C., reacting for 130 s to form double-sided mirror polishing, and the reflectance of the treated N-type crystalline silicon substrate 1 is 36%. Complete the battery structure of this step as figure 1 shown.

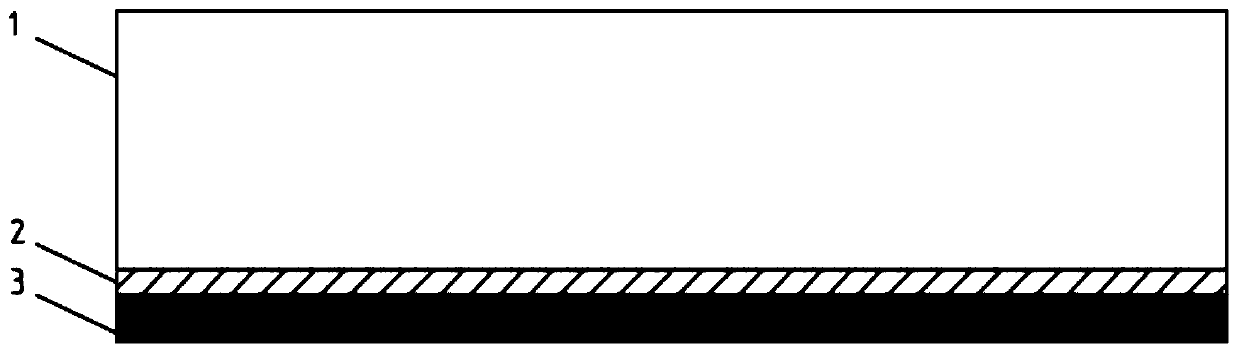

[0070] (2) On the back surface of the N-type crystalline silicon substrate 1, a thermal oxidation method is used to prepare a tunneling oxide layer 2 with silicon dioxide as a material. The thickness of the tunneling oxide layer 2 is nm. On the tunneling oxide layer 2, first The polysilicon layer is prepared by low-pressure chemical deposition, the deposition temperature is 600° C., and the thickness of the polysilicon layer is 100 nm; then, the polysilicon is doped and annealed by ion implantation to for...

Embodiment 2

[0078] (1) Take an N-type crystalline silicon substrate 1 with a resistivity of 1Ω·cm and a thickness of 170 μm, and place the N-type crystalline silicon substrate 1 with a resistivity of 1Ω·cm and a thickness of 170 μm in a KOH solution with a mass concentration of 20 wt % , at a temperature of 90° C., reacting for 200 s to form double-sided mirror polishing, and the reflectance of the treated N-type crystalline silicon substrate 1 is 39%. Complete the battery structure of this step as figure 1 shown.

[0079] (2) HNO is used on the back surface of the N-type crystalline silicon substrate 1 3 The oxidation method uses silicon dioxide as the material to prepare the tunneling oxide layer 2. The thickness of the tunneling oxide layer 2 is 2nm. On the tunneling oxide layer 2, a polysilicon layer is first prepared by low-pressure chemical deposition. The thickness of the layer is 200nm; then the polysilicon is doped by ion implantation and annealed to form the phosphorus-doped p...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More