Solar cell and preparation method thereof

A solar cell and electrode technology, applied in circuits, photovoltaic power generation, electrical components, etc., can solve problems such as damage to the borosilicate glass layer and overetching of silicon wafers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

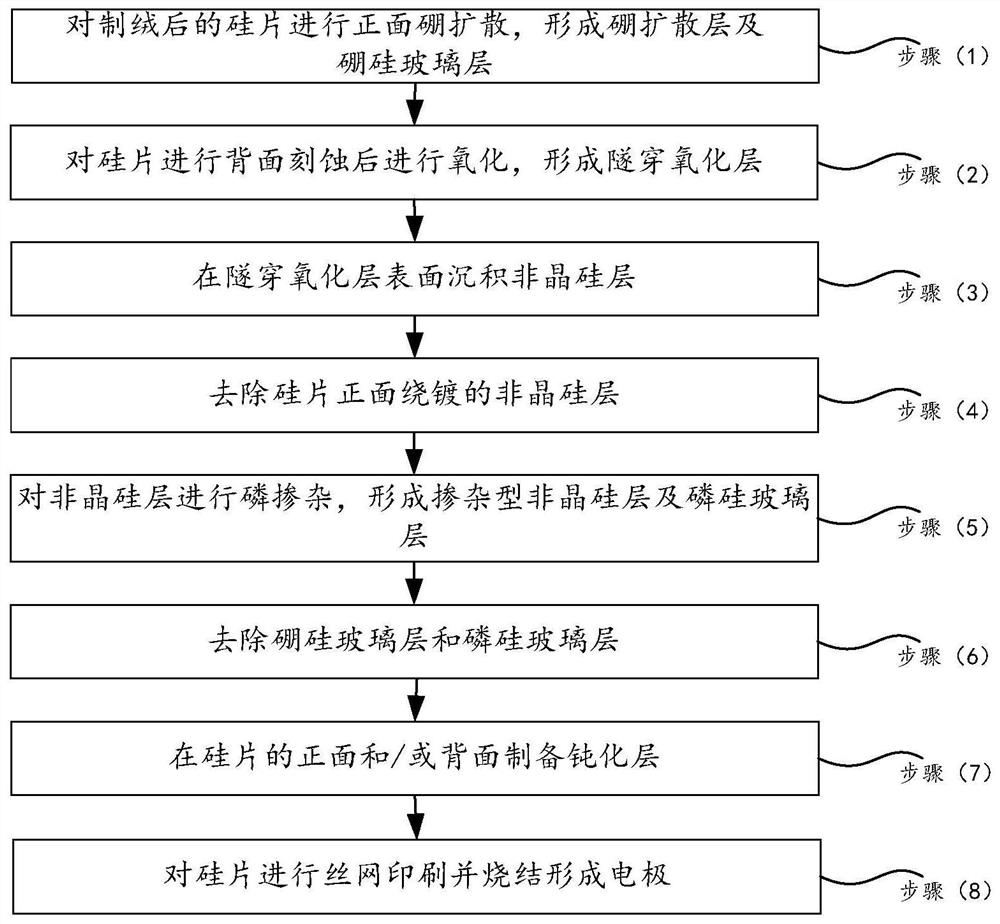

[0035] figure 1 A flow chart of a method for preparing a solar cell provided in an embodiment of the present application, such as figure 1 As shown, the application provides a solar cell preparation method, comprising the following steps:

[0036] Step (1): performing boron diffusion treatment on the front side of the textured silicon wafer to form a boron diffusion layer and a borosilicate glass (BSG) layer;

[0037] Step (2): performing back etching on the silicon wafer and then oxidizing to form a tunnel oxide layer;

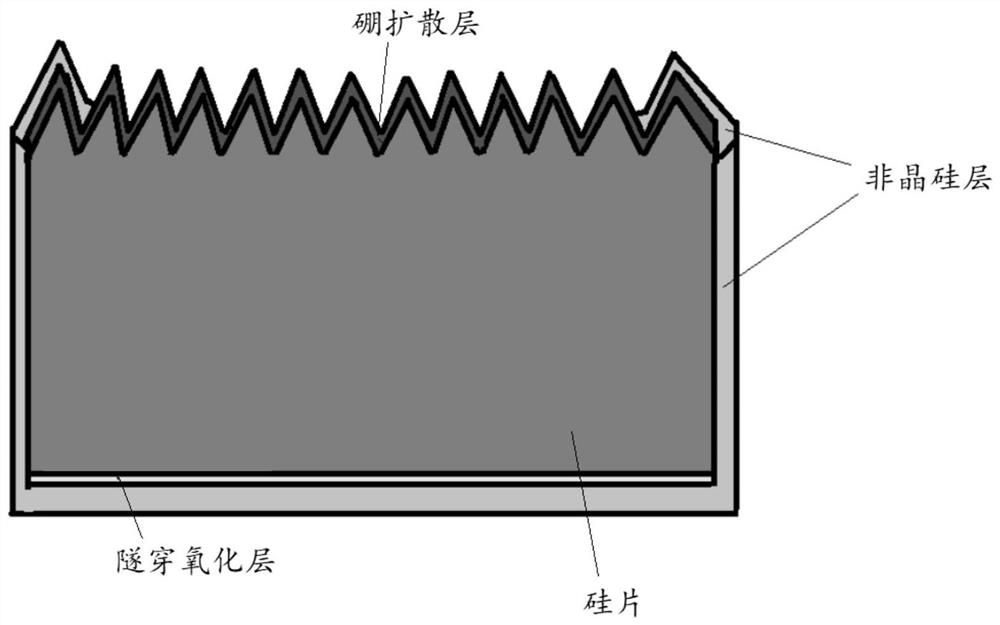

[0038] Step (3): Depositing an amorphous silicon layer on the surface of the tunnel oxide layer;

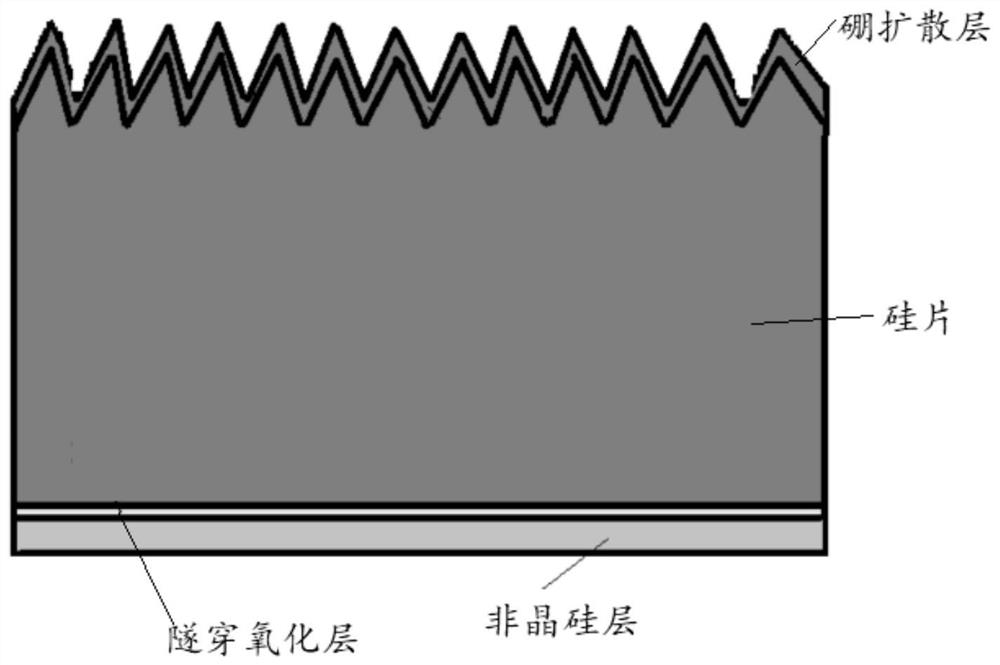

[0039] Step (4): removing the amorphous silicon layer coated on the front side of the silicon wafer;

[0040] Step (5): Doping the amorphous silicon layer with phosphorus to form a doped amorphous silicon layer and a phosphosilicate glass layer (PSG), and the doped amorphous silicon layer and the tunnel oxide layer form a TopCon structure;

[0041] Step (6) ...

Embodiment 1

[0067] Step (0): Texturing the front and back of the N-type crystalline silicon wafer;

[0068] Step (1): performing boron diffusion treatment on the front side of the silicon wafer to form a boron diffusion layer and a borosilicate glass (BSG) layer. At this time, the boron diffusion process will activate the doped boron atoms, making the silicon wafer change from microcrystalline phase to polycrystalline silicon phase.

[0069] Step (2): After etching the back side of the silicon wafer, it is oxidized by a low-pressure chemical vapor deposition method to form a tunnel oxide layer. Specifically, the raw material of the tunneling oxide layer is silicon dioxide, and the thickness of the tunneling oxide layer is 2 nm.

[0070] Step (3): Depositing an amorphous silicon layer on the surface of the tunnel oxide layer, the deposition temperature of the amorphous silicon is 550° C., and the thickness of the amorphous silicon layer is 150 nm;

[0071] Step (4): Clean the silicon waf...

Embodiment 2

[0077] Step (0): Texturing the front and back of the N-type crystalline silicon wafer;

[0078] Step (1): performing boron diffusion treatment on the front side of the silicon wafer to form a boron diffusion layer and a borosilicate glass (BSG) layer. At this time, the boron diffusion process will activate the doped boron atoms, making the silicon wafer change from microcrystalline phase to polycrystalline silicon phase.

[0079] Step (2): After etching the back side of the silicon wafer, it is oxidized by a low-pressure chemical vapor deposition method to form a tunnel oxide layer. Specifically, the raw material of the tunneling oxide layer is silicon dioxide, and the thickness of the tunneling oxide layer is 1 nm.

[0080] Step (3): Depositing an amorphous silicon layer on the surface of the tunnel oxide layer, the deposition temperature of the amorphous silicon is 560° C., and the thickness of the amorphous silicon layer is 120 nm;

[0081] Step (4): Use the prepared mixe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More