Junction field effect transistor and preparation method thereof

A field-effect transistor and junction technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as general stability, lack of exploration and innovation, and general device performance, so as to ensure purity and reduce sub- Threshold swing, effect of suppressing interface defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

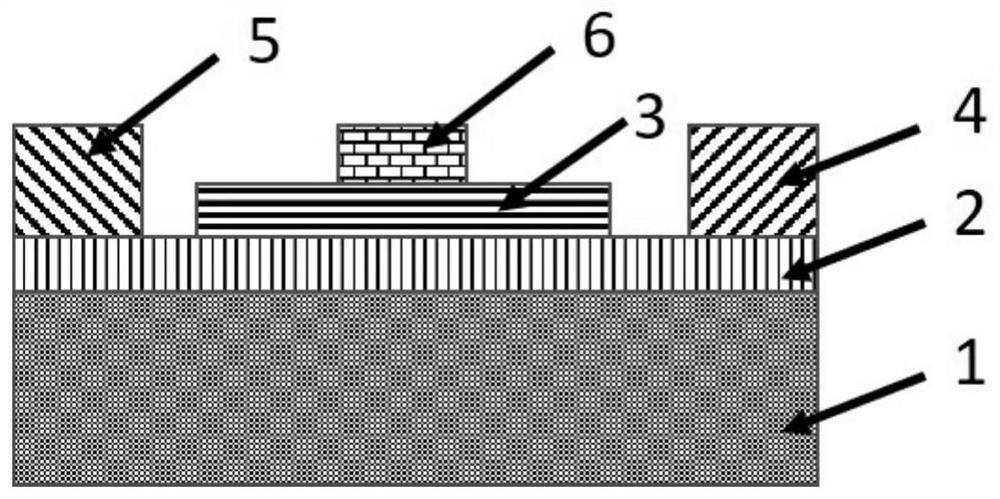

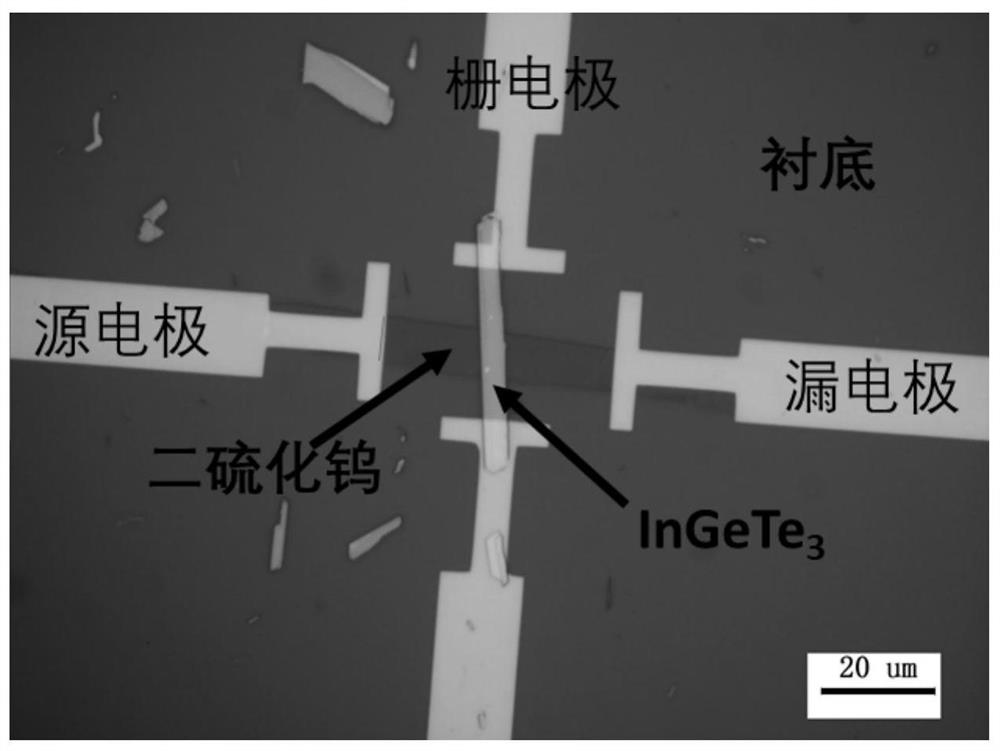

[0032] The thickness of the tungsten disulfide thin film in this embodiment is 10nm, InGeTe 3 The thickness of the film was 150 nm.

[0033] In the junction field effect transistor prepared in this embodiment, the substrate is Si / SiO 2 , the source electrode, the drain electrode and the top gate electrode are Cr / Au, the thickness of which is Cr: 10nm, Au: 50nm.

[0034] The specific preparation process is:

[0035] (1) Select a thermally oxidized silicon wafer as the substrate, first use ethanol, acetone, and deionized water to ultrasonically for 5 minutes, then heat-treat the substrate on a heating platform at 300°C for 1 hour, and store it in a dry environment;

[0036] (2) Prepare Scotch tape, put WS 2 The single crystal was repeatedly peeled and glued on Scotch tape until the surface of the tape had no obvious ups and downs, and then the tape was pasted on the surface of the silicon oxide substrate and pressed tightly. After 6 hours, the tape was removed, and the desire...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More