Coating carrier and method for increasing TCO coating area of heterojunction solar cell by using same

A solar cell and heterojunction technology, which is applied in the field of solar energy, can solve problems such as mask offset, front-back short-circuit, poor conductivity of amorphous silicon, etc., and achieve the effect of increasing the film-forming area and improving the conversion efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

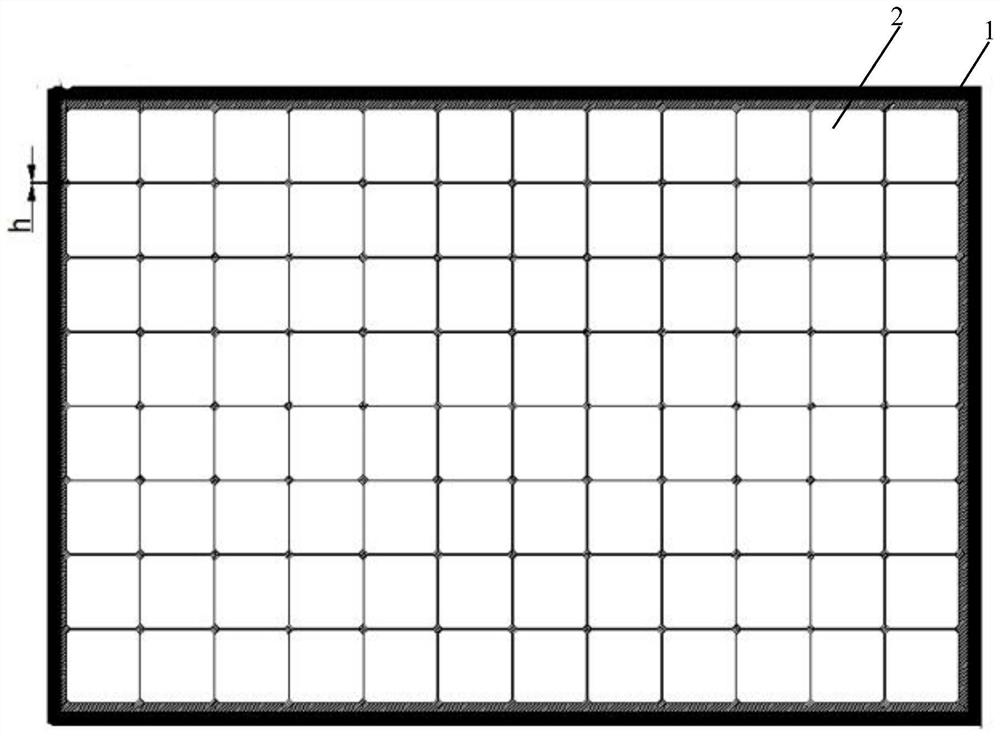

[0044]The coating carrier includes a carrier body 1 and a plurality of placement parts 2 for containing silicon wafers, and the placement parts 2 are evenly distributed along the longitudinal and transverse directions of the carrier body;

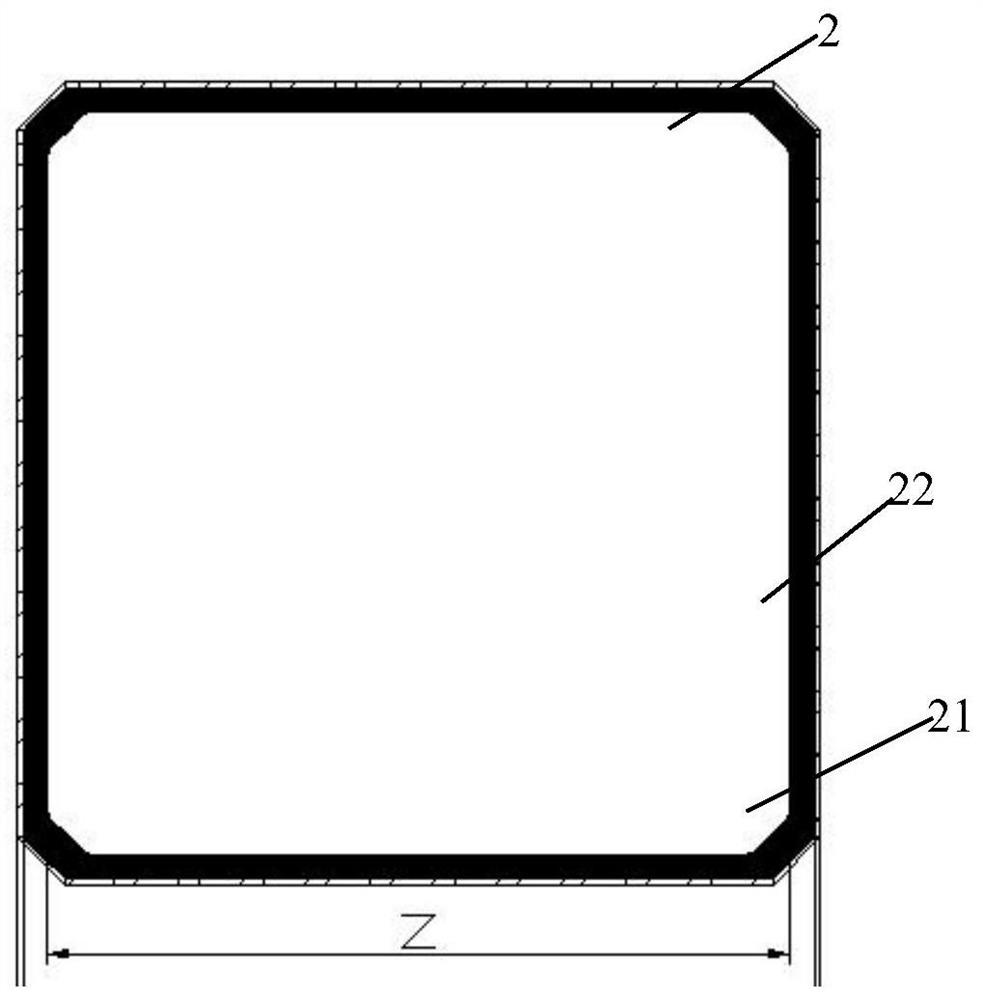

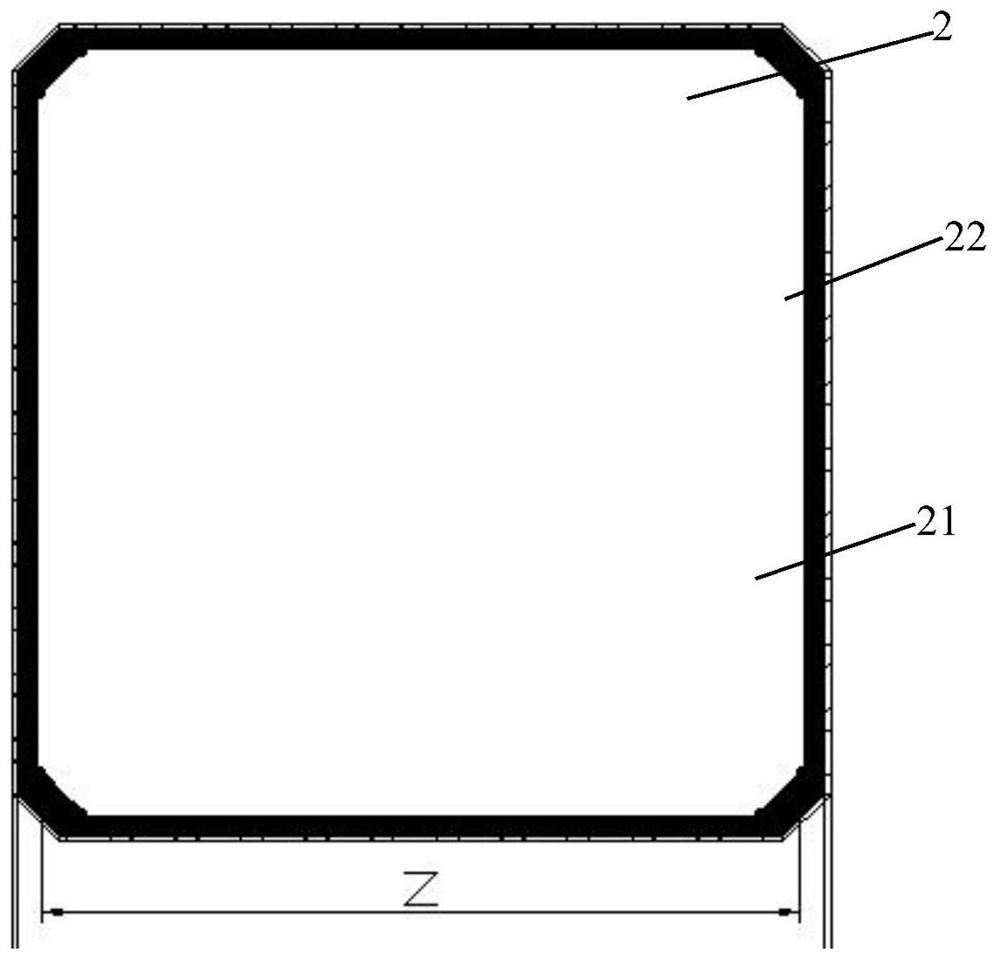

[0045] The placing part 2 includes a first frame body 22 and a second frame body 21, and the first frame body 22 is arranged outside the second frame body 21;

[0046] A plurality of support points 23 are oppositely arranged on the inner wall of the second frame body 21 .

[0047] In one embodiment, support points 23 are set at the inner four corners of the second frame body 21 or support points 23 are set at the opposite corners, the distance between the two opposite inner side walls of the second frame body 21 is Z, and the side length of the silicon wafer is A. Z≤A-0.2mm. If it exceeds the range value defined above, it will easily cause leakage of the battery device.

[0048] In one embodiment, when the support points 23 are set on the...

Embodiment 2

[0059] A method for increasing the TCO coating area of a heterojunction solar cell comprising the following steps:

[0060] (1) Perform texturing treatment on N-type monocrystalline silicon wafers with a thickness of 180 μm to form a pyramid textured surface, remove impurity ions and clean the surface;

[0061] (2) Utilizing plasma chemical vapor deposition to prepare double intrinsic amorphous silicon layers on the front and back sides of the crystalline silicon wafer obtained in step (1);

[0062] (3) Prepare a doped amorphous silicon layer on the double-sided intrinsic amorphous silicon layer; one side of the doped amorphous silicon layer is doped with P to form N-type doped amorphous silicon, and the other side is doped with B to form P-type doped Heteromorphic silicon;

[0063] (4) Place the silicon chip made in step (3) on the placement part 2 of the coating carrier, and then prepare a double-sided conductive film layer and a mask area on the doped amorphous silicon l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More