Semiconductor device and forming method thereof

A technology for semiconductors and devices, applied in the field of semiconductor devices and their formation, can solve the problems that the electrical performance of multi-gate transistors needs to be improved, the constraints of photolithography process are difficult to overcome, and the multi-gate transistors are reduced, so as to improve electrical performance and reduce parasitic capacitance. , the effect of reducing difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

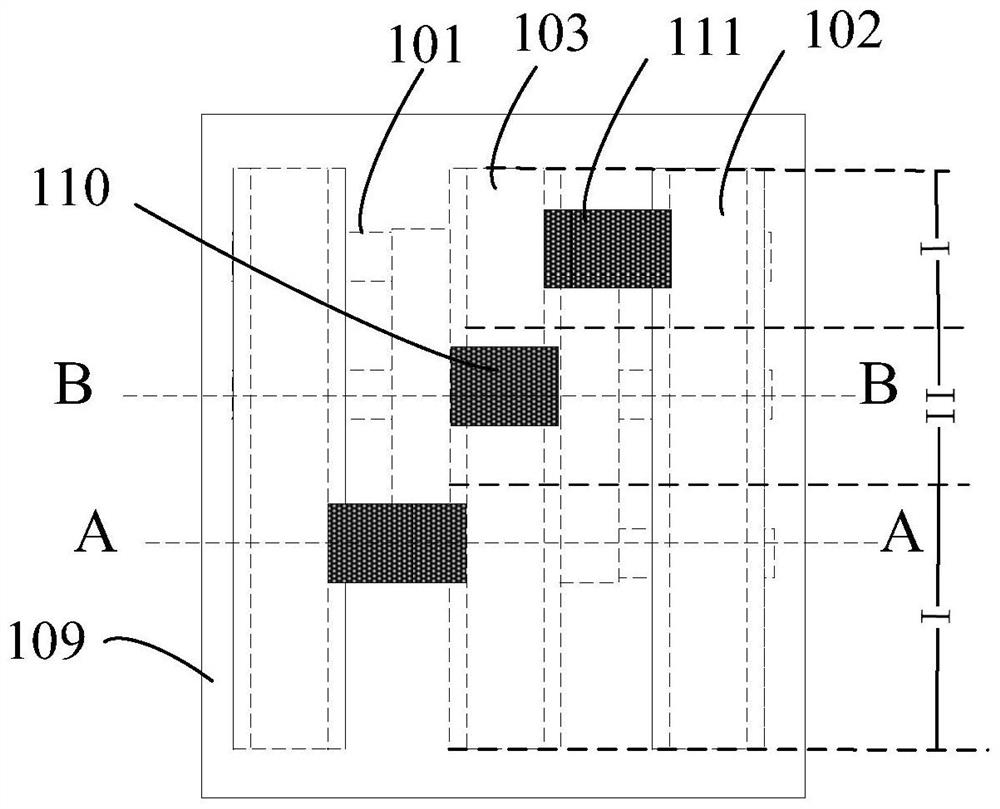

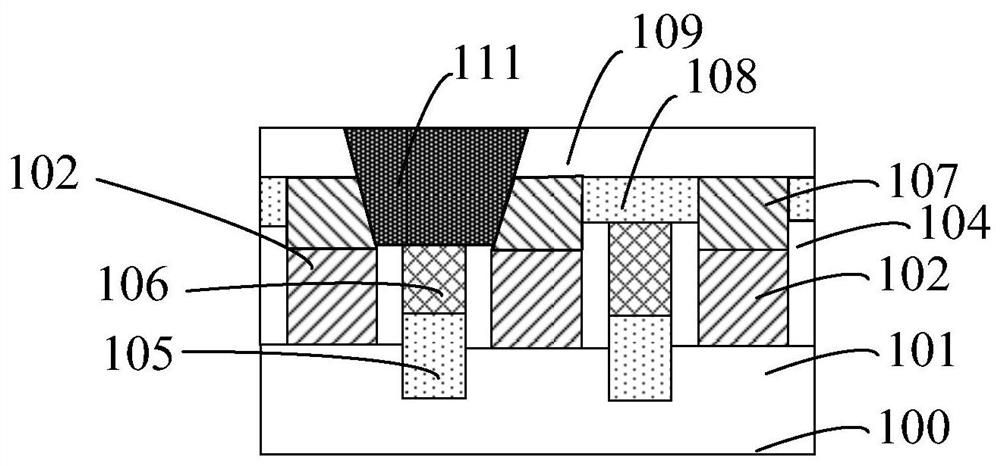

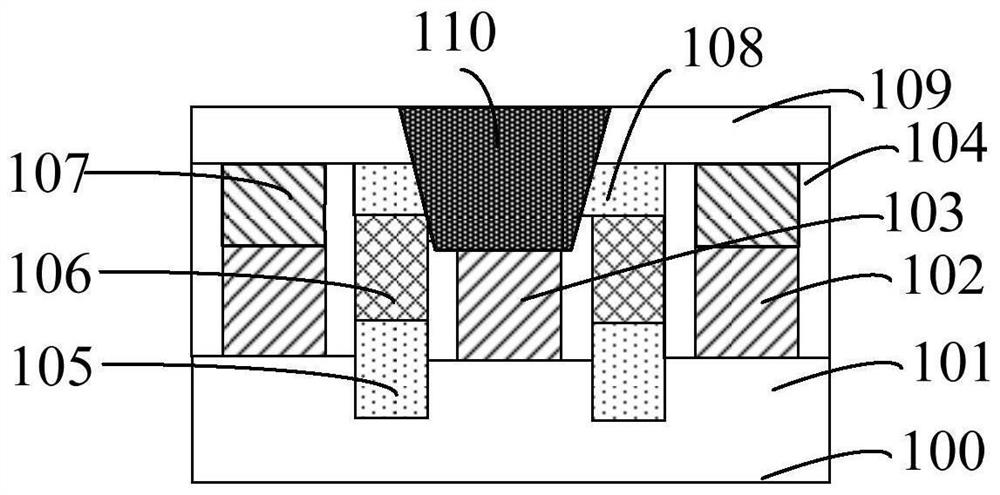

[0040] Figure 4 to Figure 27 It is a structural schematic diagram of the formation process of a semiconductor device according to the first embodiment of the present invention.

[0041] Please refer to Figure 4 , providing a substrate 200 .

[0042] In this embodiment, the base 200 includes a substrate 201 and a plurality of discretely arranged fins 202 located on the substrate 201 , and the fins 202 extend along the second direction X.

[0043] In other embodiments, the fin portion 202 may not be formed on the substrate 201 .

[0044] In this embodiment, the material used for the substrate 201 is single crystal silicon.

[0045] In other embodiments, the substrate 201 may also be polysilicon or amorphous silicon. The material of the substrate 201 may also be germanium, silicon germanium, gallium arsenide, silicon on insulator (SOI), germanium on insulator (GOI) and other semiconductor materials.

[0046] In this embodiment, the material of the fin portion 202 is silico...

no. 2 example

[0151] The difference between this embodiment and the first embodiment is that the opening exposes the initial second hard mask layer on one side of the end of the gate structure and the initial first hard mask layer on the end of the gate structure. A hard mask layer, please refer to the Figure 28 to Figure 41 .

[0152] For the process from providing the substrate to forming the initial first hard mask layer and the initial second hard mask layer, please refer to the first embodiment Figure 4 to Figure 13 the process of.

[0153] Please refer to Figure 28 , forming a patterned layer 219 on the initial first hard mask layer 215 and the initial second hard mask layer 218, the patterned layer 219 has an opening 228, and the opening 228 exposes the gate The initial second hard mask layer 218 on the side of the end I of the structure 213 and the initial first hard mask layer 215 on the end I of the gate structure 213 .

[0154] In this embodiment, the opening 228 also expo...

PUM

| Property | Measurement | Unit |

|---|---|---|

| relative permittivity | aaaaa | aaaaa |

| relative permittivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com