Process integration method for integrating high-voltage CMOS (complementary metal oxide semiconductor) in logic process

An integrated method and process technology, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as STI depth should not be too deep, device failure, defects, etc., to improve doping uniformity, eliminate defects and positions Wrong, the effect of improving the withstand voltage performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

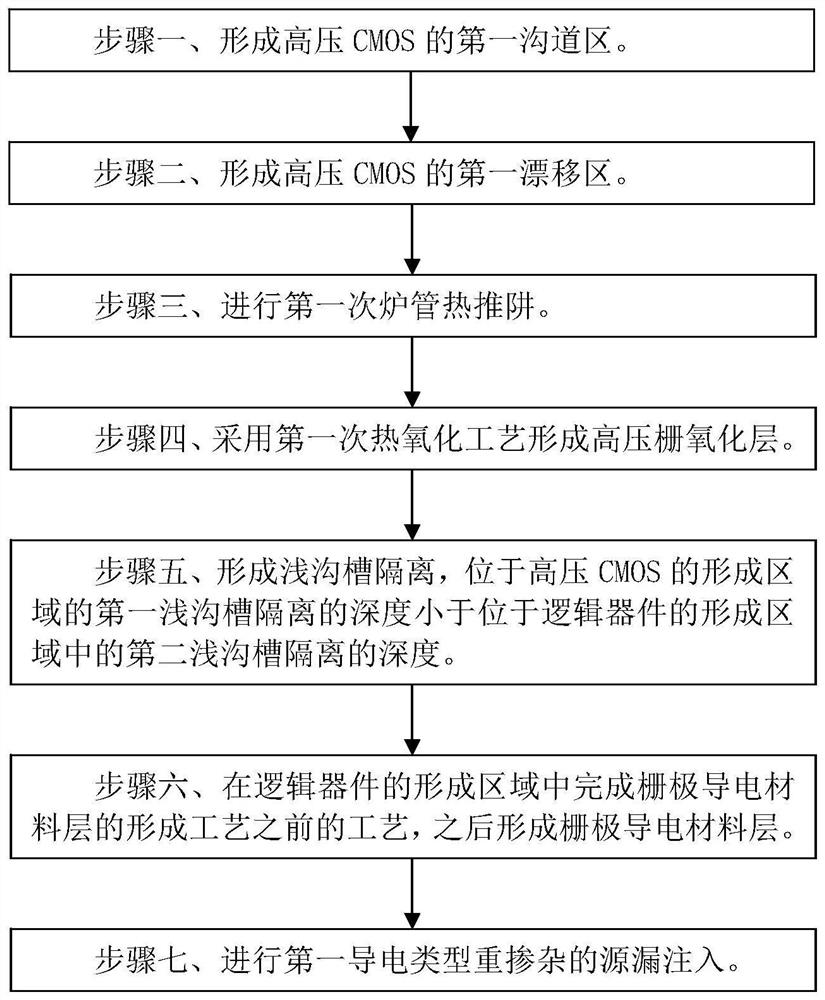

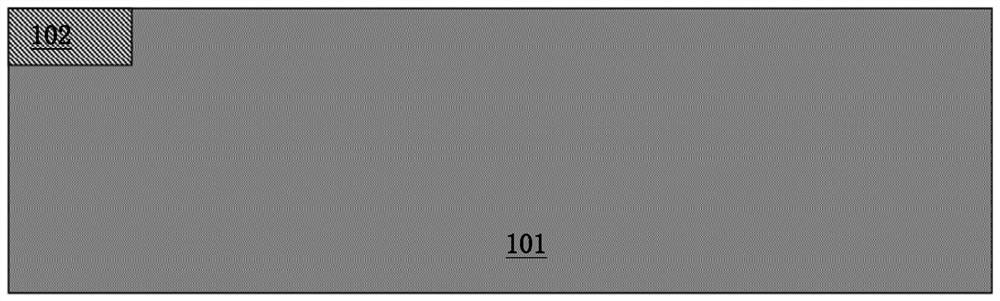

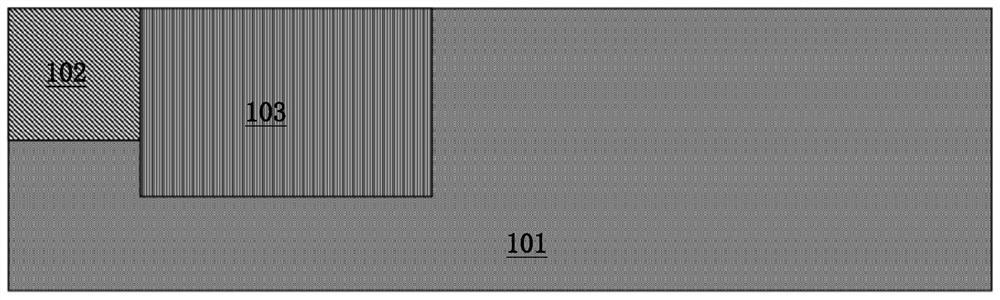

[0052] Such as figure 1 As shown, it is a flowchart of a process integration method for integrating a high-voltage CMOS in a logic process according to an embodiment of the present invention; as Figure 2A to Figure 2N Shown is a schematic diagram of the device structure in each step of the process integration method for integrating high-voltage CMOS in the logic process of the embodiment of the present invention; the operating voltage of the logic device in the process integration method for integrating high-voltage CMOS in the logic process of the embodiment of the present invention The operating voltage of CMOS, including the following steps:

[0053] Step 1, such as Figure 2A As shown, the first channel region 102 doped with the second conductivity type is formed in the semiconductor substrate 101 in the selected region of the high voltage CMOS formation region 201 . The high voltage CMOS formation region 201 is in Figure 2C marked with curly brackets.

[0054] In th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More