Gamma gate heterojunction field effect transistor and preparation method thereof

A heterojunction field effect and transistor technology, applied in the field of microelectronics, can solve the problems of reducing device stability, reducing device yield, and increasing device feedback capacitance, so as to reduce gate leakage current, increase breakdown voltage, The effect of reducing gate leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

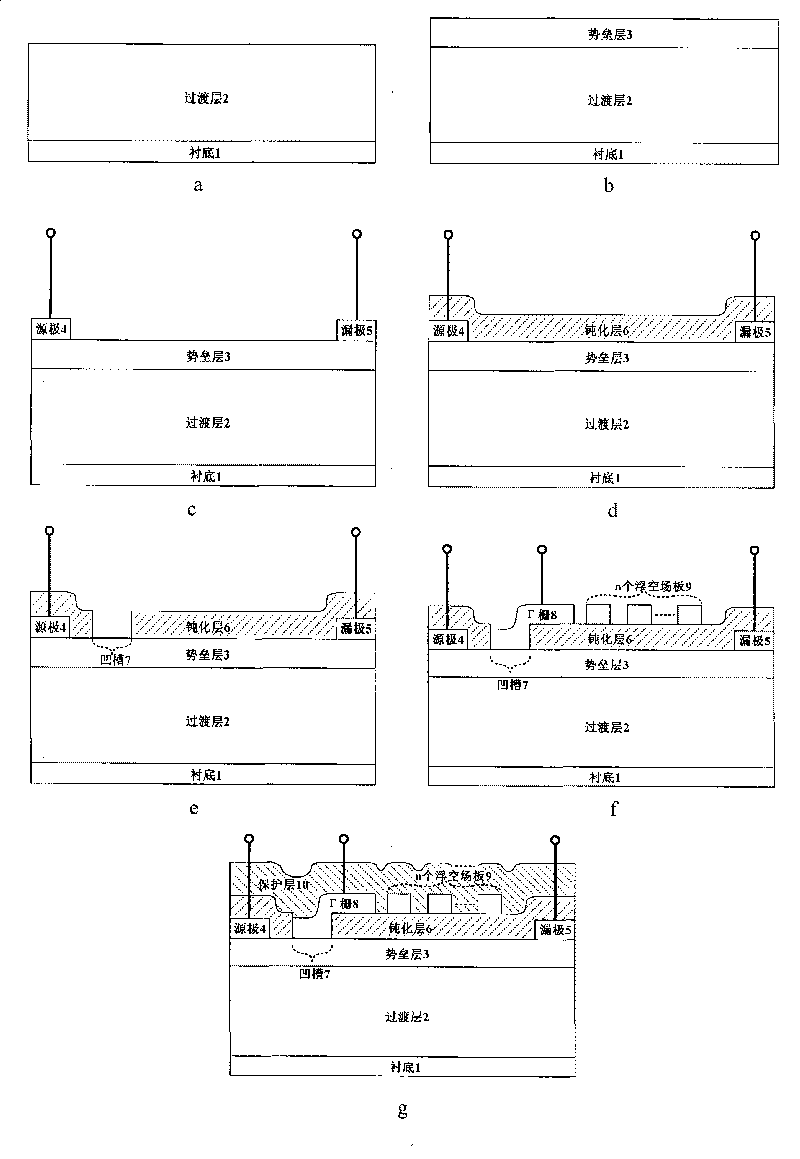

Embodiment 1

[0054] The production substrate is sapphire, and the passivation layer is SiO 2 , the protective layer is SiO 2 , the Γ gate and each floating field plate are Mo / Au metal combination Γ gate heterojunction field effect transistors, the process is:

[0055] 1. Using metal organic chemical vapor deposition technology to epitaxially undoped transition layer 2 with a thickness of 1 μm on the sapphire substrate 1, the transition layer is composed of AlN material with a thickness of 37 nm and GaN material with a thickness of 0.963 μm from bottom to top constitute. The process conditions used for the epitaxial lower layer AlN material are: temperature 595 ° C, pressure 170 Torr, hydrogen gas flow rate 4800 sccm, ammonia gas flow rate 4800 sccm, aluminum source flow rate 40 μmol / min; the process conditions used for the epitaxial upper layer GaN material are: temperature 1060°C, pressure 170 Torr, hydrogen flow rate 4800 sccm, ammonia gas flow rate 4800 sccm, gallium source flow rate 17...

Embodiment 2

[0063] The substrate is silicon carbide, the passivation layer is SiN, the protective layer is SiN, the Γ gate and each floating field plate are Ni / Au metal combination Γ gate heterojunction field effect transistor, and the process is:

[0064] 1. An undoped transition layer 2 with a thickness of 1.5 μm is epitaxially formed on a silicon carbide substrate 1 by metal-organic chemical vapor deposition technology. Made of GaN material. The process conditions used for the epitaxial lower layer AlN material are: temperature 1030°C, pressure 175 Torr, hydrogen gas flow rate 4900 sccm, ammonia gas flow rate 4900 sccm, aluminum source flow rate 14 μmol / min; the process conditions for the epitaxial upper layer GaN material are: temperature 1030°C, pressure 175 Torr, hydrogen flow rate 4900 sccm, ammonia gas flow rate 4900 sccm, gallium source flow rate 170 μmol / min.

[0065] 2. Deposit an undoped barrier layer 3 with a thickness of 30nm on the GaN transition layer 2 by metal organic c...

Embodiment 3

[0072] The production substrate is silicon, the passivation layer is SiN, and the protective layer is Al 2 o 3 , the Γ gate and each floating field plate are Pμ / Au metal combined Γ gate heterojunction field effect transistors, and the process is:

[0073] 1. Using metal organic chemical vapor deposition technology to epitaxially undoped transition layer 2 with a thickness of 5 μm on the silicon substrate 1, the transition layer is composed of AlN material with a thickness of 130 nm and GaN material with a thickness of 4.87 μm from bottom to top constitute. The process conditions used for the epitaxial lower layer AlN material are: temperature 870 ° C, pressure 178 Torr, hydrogen gas flow rate 5000 sccm, ammonia gas flow rate 5000 sccm, aluminum source flow rate 40 μmol / min; the process conditions used for the epitaxial upper layer GaN material are: temperature 1060°C, pressure 178 Torr, hydrogen flow rate 5000 sccm, ammonia gas flow rate 5000 sccm, gallium source flow rate 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More