Cleaning method after opening etching

An etching and wet cleaning technology, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of damaging the low dielectric constant dielectric layer, changing, and reducing the process capacity, so as to improve the process yield and simplify the process. Process steps, the effect of reducing process costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

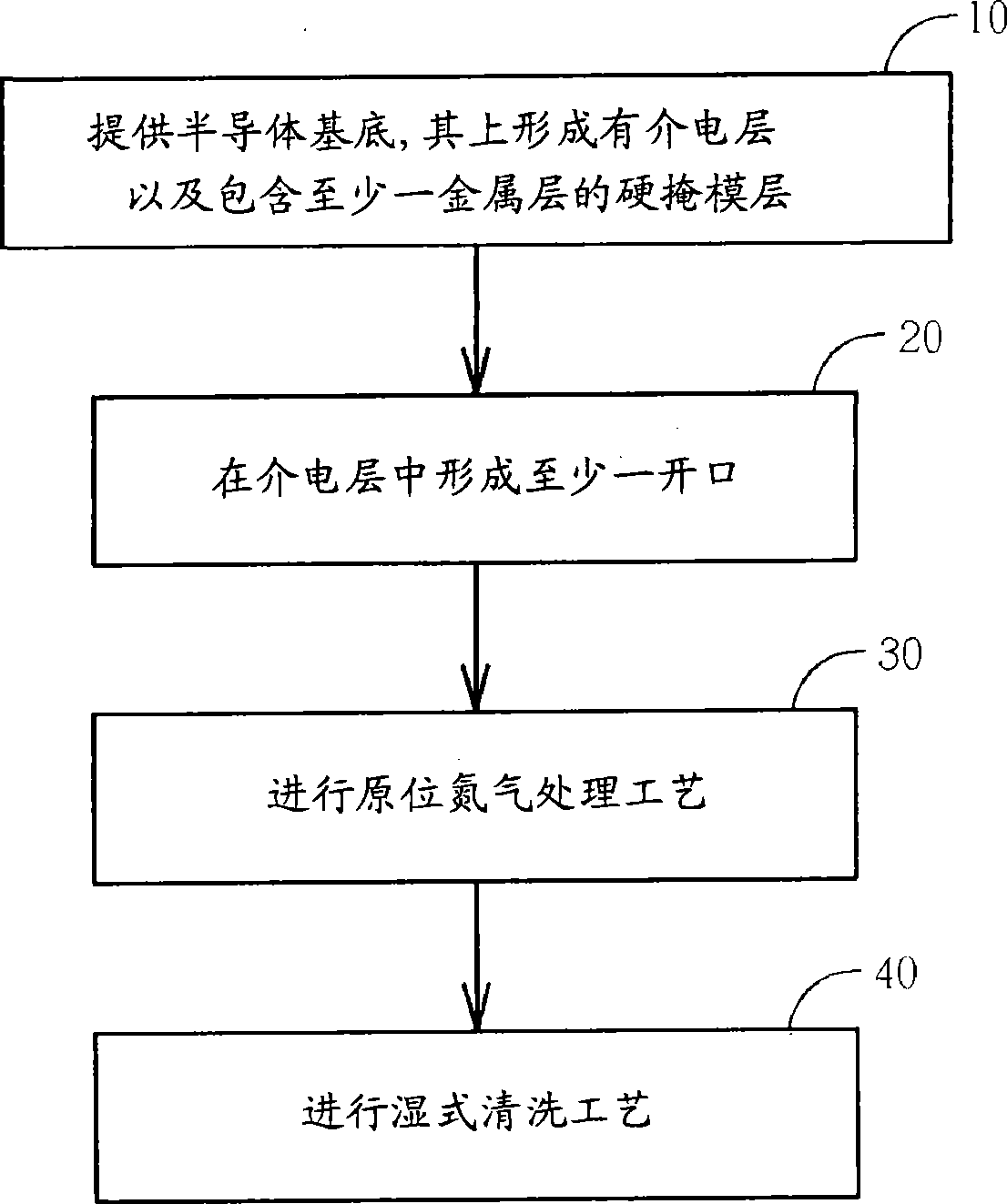

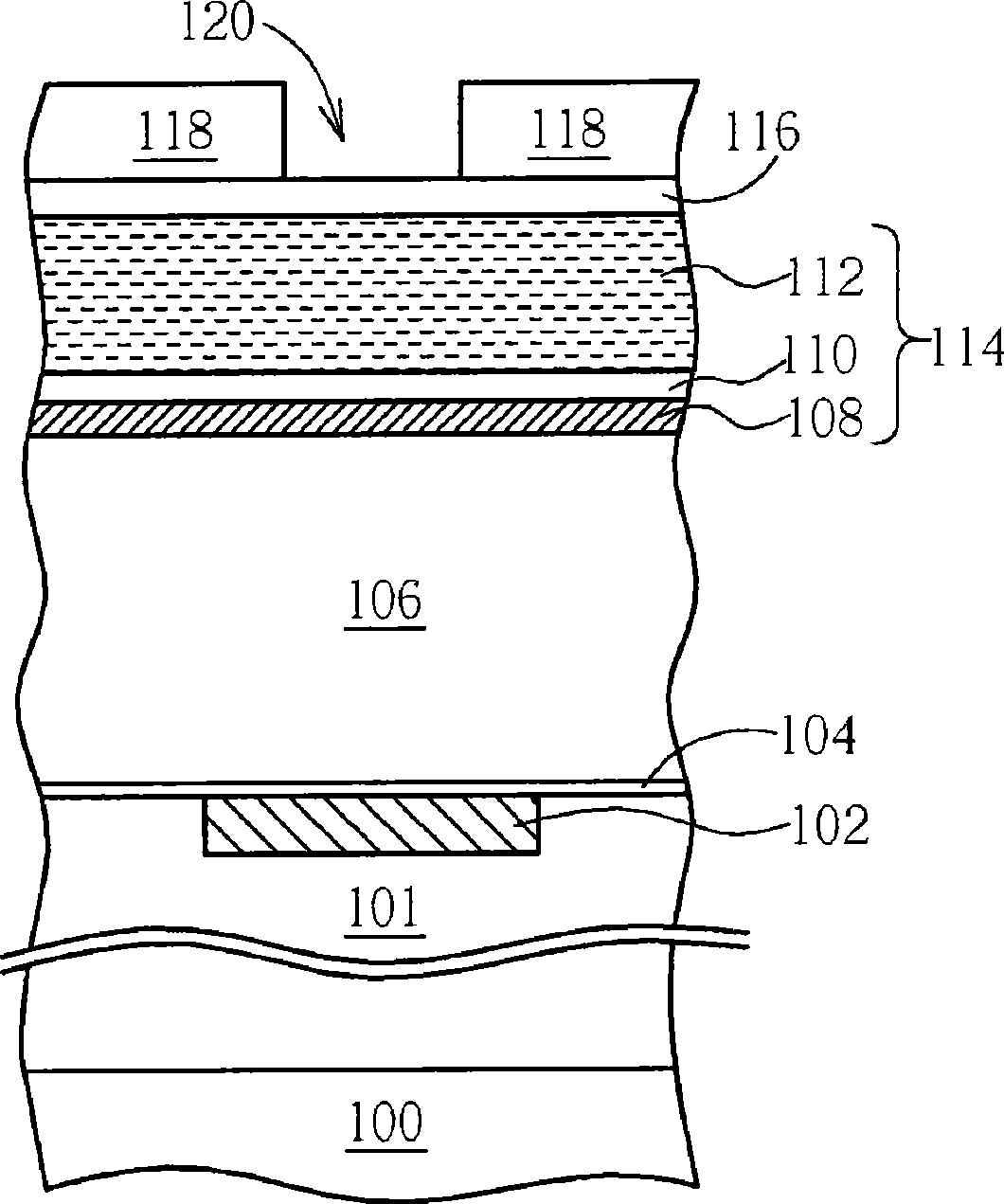

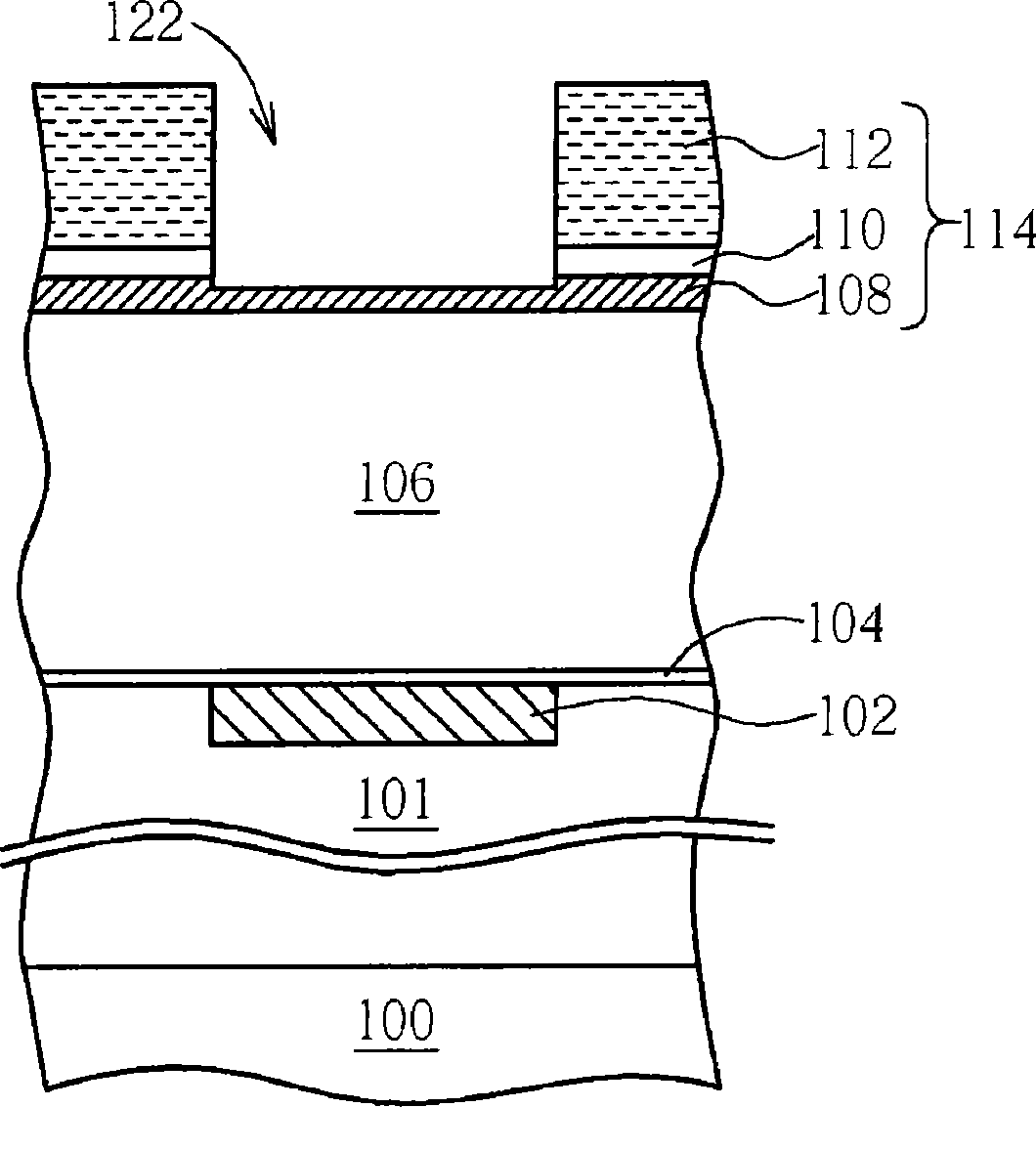

[0037] Please refer to figure 1 , figure 1 It is a flowchart of the cleaning method after opening etching in the present invention. Such as figure 1As shown, in step 10, first provide a semiconductor substrate, such as a silicon substrate or a silicon-on-insulator (SOI) substrate, etc., on which a dielectric layer and a hard mask layer are formed, wherein the hard The mask layer includes at least one metal layer. The semiconductor substrate may also include at least one functional element, such as a Metal Oxide Semiconductor (MOS) transistor. The dielectric layer is a low dielectric constant dielectric layer, such as carbon-doped oxide (carbon-doped oxide; CDO), organic silicon glass (OSGs), fluorine-containing silicon dioxide (FSGs), or ultra-low dielectric constant ( Ultra low-k; k<2.5) and other material layers; methods for forming low-k dielectric layers include spin-coating (spin-coating) process, plasma-enhanced chemical vapor deposition (plasma-enhanced chemical vap...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More