Three-sided silicified gate metallic oxide semiconductor field effect transistor and preparation method thereof

An oxide semiconductor and field effect transistor technology, applied in the field of semiconductor devices and their fabrication processes, can solve the problems of increasing gate resistance, limiting the improvement and upgrading of LDMOSFET device performance, and reducing the gate resistance of the device and optimizing the device. performance, the effect of good device performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] Firstly, taking the preparation of a MOSFET with low gate resistance as an example, the specific implementation of the three-side silicided gate metal silicide solution proposed by the present invention and the device fabrication process flow are introduced.

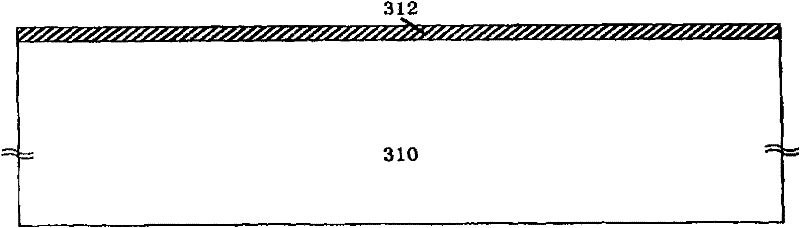

[0035] 1. As shown in FIG. 3.1 , a gate dielectric (some dielectric) layer 312 is thermally grown or deposited on a silicon substrate 310 of the first conductivity type. Before or after forming the gate dielectric layer 312 , ion implantation is performed into the substrate 310 to achieve the purpose of adjusting the threshold voltage of the finally fabricated device.

[0036] 2. As shown in Figure 3.2, deposit a polysilicon layer 314 on the gate dielectric layer 312, and make it a heavily doped polysilicon layer by in-situ doping during deposition or ion implantation after deposition.

[0037] 3. As shown in Figure 3.3, heavy doping is formed by photolithography and etching (the doping concentration is 1×10 19 / ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More