Gate stack structure for semiconductor flash memory device and preparation method thereof

A flash memory device and gate stack technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve the problems of slow operation speed and high operating voltage, increase electric field strength, improve storage density, and reduce operation. The effect of voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

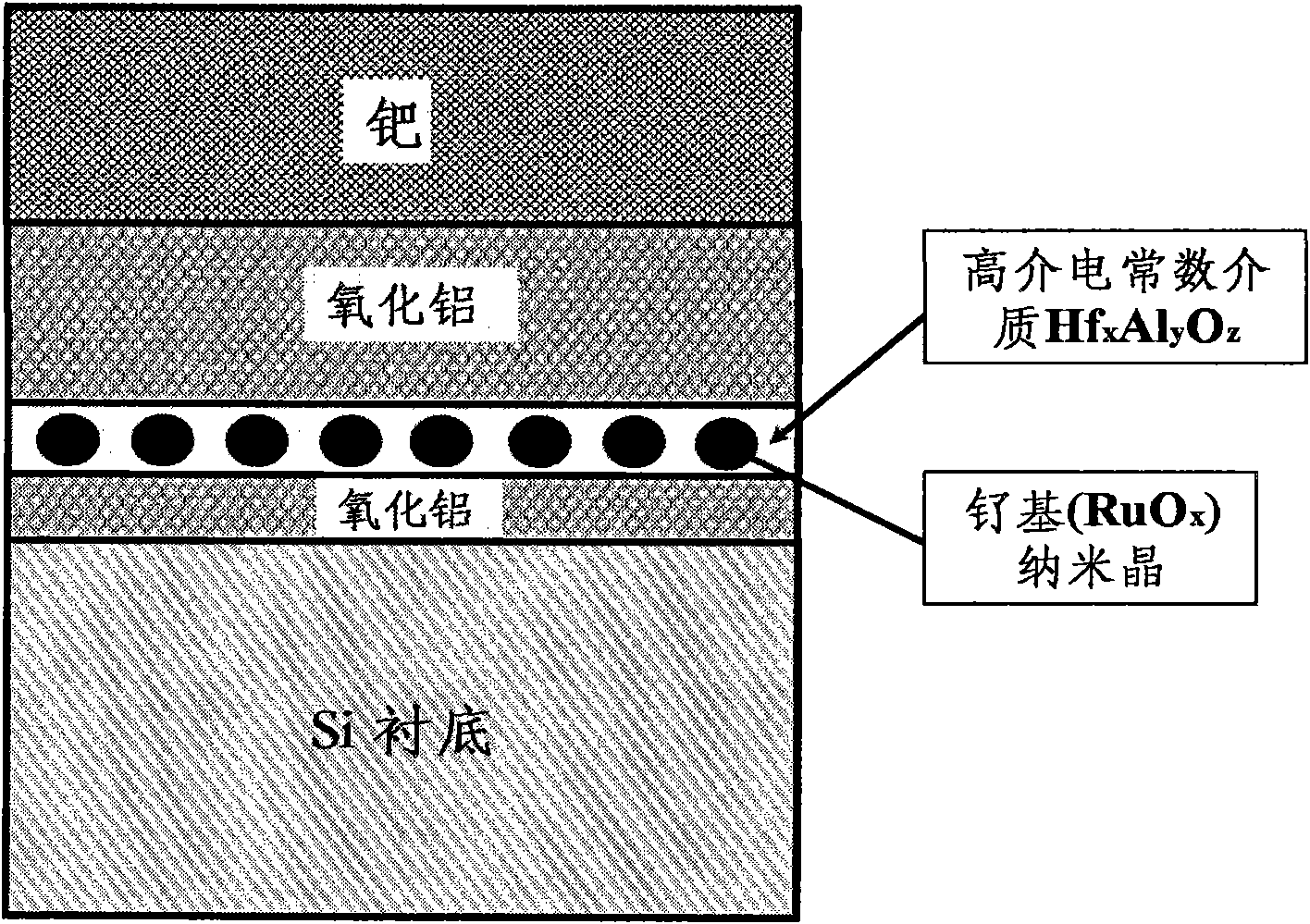

[0038] The preparation method of the novel gate stack structure flash storage capacitor proposed by the present invention is as follows:

[0039] (1) A P-type single crystal silicon wafer with (100) crystal orientation is used as the substrate, and the resistivity of the silicon wafer is 8-12 ohm·cm. Silicon wafers are first cleaned as standard, and the residual native oxide layer is removed with dilute hydrofluoric acid.

[0040] (2) Tunneling layer Al 2 o 3 The formation of: using trimethylaluminum and water vapor as the reaction source, the method of atomic layer deposition is used to grow Al 2 o 3 For thin films, the substrate temperature is controlled within the range of 250-350°C. Al 2 o 3 The thickness of the tunneling layer is controlled within the range of 5-10 nanometers.

[0041] (3) Nanocrystalline RuO in the heterogeneous charge-trapping layer x The formation: using magnetron sputtering deposition method, in Al 2 o 3 Deposit an ultra-thin metal ruthenium...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com