Diffusion method used for crystalline silicon solar battery

A technology of solar cells and diffusion methods, which is applied in the field of diffusion of crystalline silicon solar cells, and can solve problems such as high series resistance of cells, unfavorable electron collection, and reduced efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

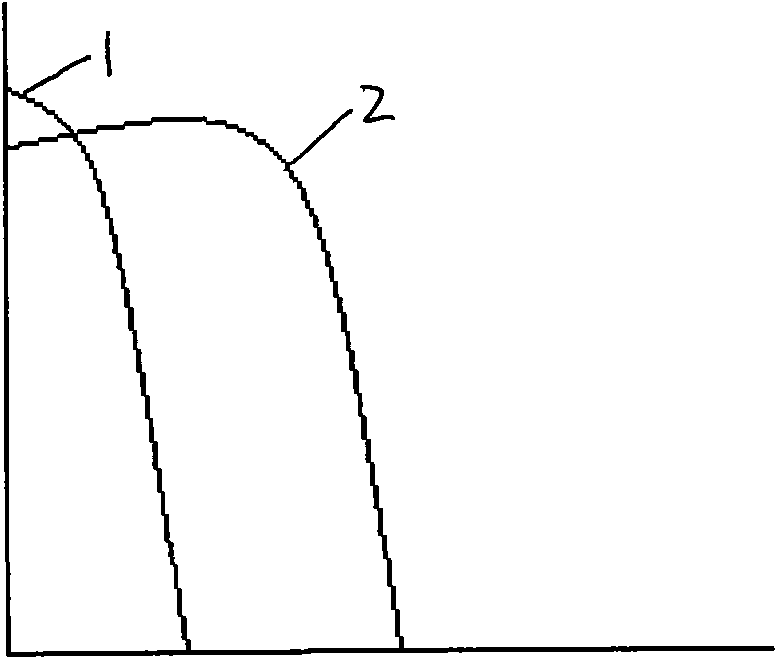

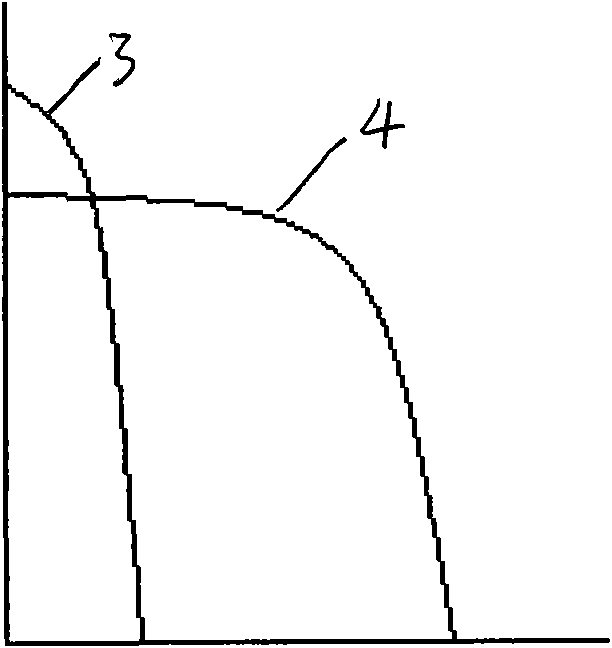

Image

Examples

Embodiment 1

[0016] Embodiment 1: This embodiment includes the following steps: 1. Put the silicon wafer into the diffusion furnace for 10 minutes. 2. Raise the temperature from 810°C to 840°C, and feed POCL at the same time 3 700sccm, O 2 200sccm, N 2 6slm, with 12min. +The temperature gradient rises in the application of temperature rise and diffusion, which increases the activity of phosphorus atoms on the surface of the silicon body, making the phosphorus atoms that enter the silicon body have stronger activity, and increases the uniformity of phosphorus diffusion on silicon wafers. 3. Stabilize at 840°C for 2 minutes, while passing O 2 300sccm, N 2 6slm. 4. Raise the temperature from 840°C to 870°C, and feed POCL at the same time 3 500sccm, O 2 300sccm, N 2 6slm, time 8min. 5. Decrease the temperature from 870°C to 800°C, and pass O at the same time 2 500sccm, N 2 6slm; the combination of cooling promotion and gettering greatly shortens the process time and improve...

Embodiment 2

[0017] Embodiment 2: This embodiment includes the following steps: 1. Put the silicon wafer into the diffusion furnace. 2. Raise the temperature from 780°C to 850°C, and feed POCL at the same time 3 1000sccm, O 2 500sccm, N 2 8slm, it took 13min. 3. Stable at 850°C for 3 minutes, while passing O 2 400sccm,N 2 9slm. 4. Raise the temperature from 850°C to 880°C, and feed POCL at the same time 3 700sccm, O 2 500sccm, N 2 8slm, with 9min. 5. Decrease the temperature from 880°C to 800°C, and pass O at the same time 2 800sccm, N 2 9slm. 6. Stabilize at 800°C for 2 minutes, and pass POCL at the same time 3 2000sccm, O 2 800sccm, N 2 10slm. 7. Take out the silicon wafer from the diffusion furnace.

Embodiment 3

[0018] Embodiment 3: This embodiment includes the following steps: 1. Put the silicon wafer into the diffusion furnace. 2. Raise the temperature from 790°C to 860°C, and feed POCL at the same time 3 600sccm, O 2 300sccm, N 2 5slm, it takes 14min. 3. Stable at 860°C for 5 minutes, while passing O 2 200 sccm, N 2 5slm. 4. Raise the temperature from 860°C to 890°C, and feed POCL at the same time 3 600sccm, O 2 200sccm, N 2 5slm, with 12min. 5. Decrease the temperature from 890°C to 800°C, and pass O at the same time 2 300sccm, N 2 5slm. 6. Stabilize at 800°C for 2 minutes, and pass POCL at the same time 3 800sccm, O 2 1000sccm, N 2 12slm. 7. Take out the silicon wafer from the diffusion furnace.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More