Highly-parallel micro flow channel chip applied to preparation of nanoparticles

A technology of micro-channels and channels, applied in the field of high-parallel micro-channel chips, can solve the problems of poor industrial application prospects, difficult high-yield products, and no increase in output, so as to achieve sample uniformity control, low cost, and low cost. The effect of preparation costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

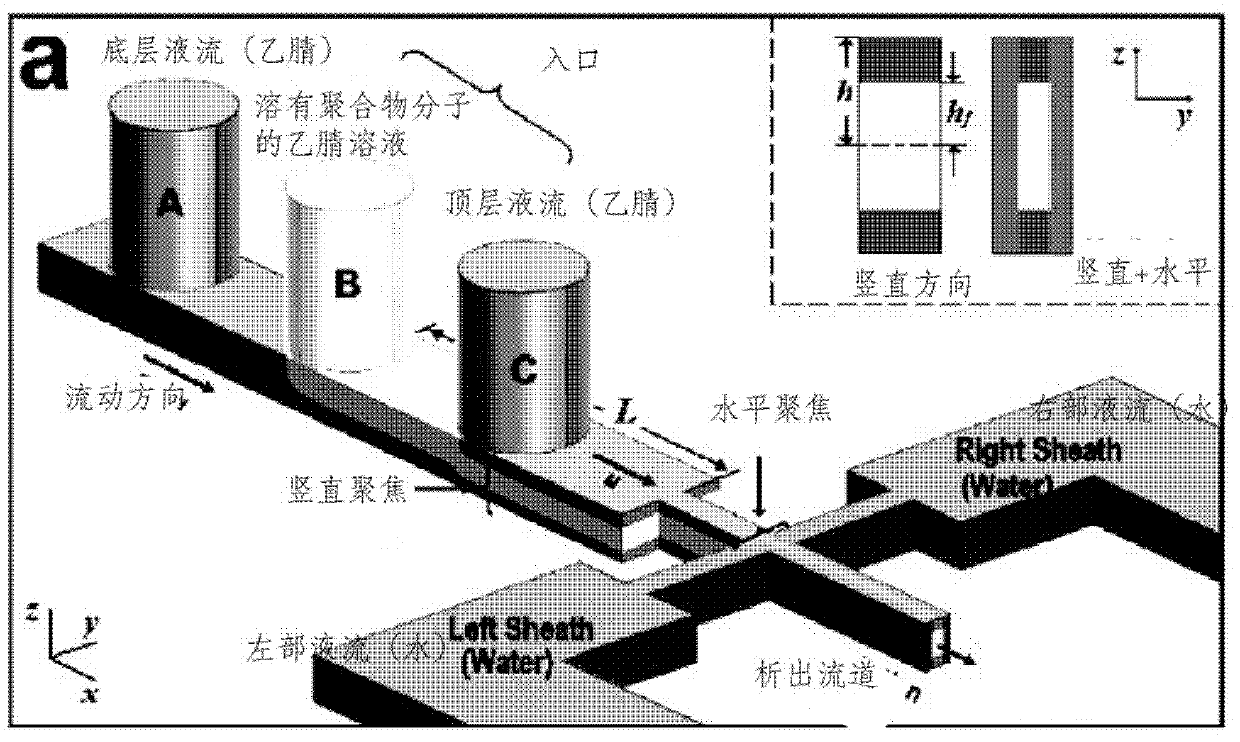

[0049] Example 1 Preparation of a three-layer parallel microfluidic chip 1:

[0050] Step 1: Photolithography process

[0051] 1) Preparation of middle layer flow channel mold: use photoresist SU83005, apply 5-10 micron photoresist on the silicon wafer with a glue throwing machine (rotation speed 3000rpm-2000rpm, time 30s), and bake at 65 degrees Celsius 1 minute, bake at 95 degrees Celsius for 5 minutes before baking, and then put it under the exposure machine for exposure. The mask used is the designed middle layer pattern ( Figure 5 ) negative version, the exposure time is 50 seconds, and the light intensity is 20mw / cm 2 ; After exposure, the sample is placed at 65 degrees Celsius for 1 minute, and then baked at 95 degrees Celsius for 5 minutes; after developing with the developer, the middle layer mold is obtained;

[0052] 2) Preparation of the top and bottom flow channel molds: use photoresist SU83025, the steps are the same as above, the pre-baking conditions are 6...

Embodiment 2

[0065] Example 2 Preparation of three-layer parallel microfluidic chip 2:

[0066] Using the method of Example 1, a three-layer parallel microfluidic channel chip was prepared with a liquid inlet line width of 300 um, 50 liquid outlets at the end of the middle layer flow channel, and 120 liquid outlets at the end of the top and bottom layers. The width of the liquid outlet of the middle channel is 20 microns, the height is 15 microns, and the line period is 100 microns; the width of the liquid outlet of the top channel and the bottom channel is 40 microns, the height is 20 microns, and the line period is 50 microns microns; the thickness of the bottom layer of PDMS is 40 microns, and the thickness of the middle layer of PDMS is 30 microns.

Embodiment 3

[0067] Example 3 Preparation of three-layer parallel microfluidic chip 3:

[0068] Adopt the method of Example 1, but replace PDMS with plexiglass PMMA, PMMA is heated and liquefied, not the same cross-linking and curing reaction as PDMS; the PDMS in step 2 of Example 1 can be changed to heating and melting at 180 degrees Celsius The final PMMA; in 5), the obtained three-layer PMMA-covered runner mold was cooled at room temperature; in step 3, the plasma bonding was changed to heating bonding at 140 degrees Celsius.

[0069] A three-layer parallel microfluidic channel chip was prepared with a liquid inlet line width of 100um, 450 liquid outlets at the end of the middle layer, and 1000 liquid outlets at the end of the top and bottom layers. The width of the liquid outlet of the middle channel is 10 microns, the height is 10 microns, and the line period is 100 microns; the width of the liquid outlet of the top channel and the bottom channel is 10 microns, the height is 5 micro...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More