Method for preparing germanium-base MOSFET grate medium

A gate dielectric, germanium-based technology, applied in the field of preparation of germanium-based MOSFET gate dielectric, to achieve the effects of improved electrical characteristics, low interface state density, and high thermal stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

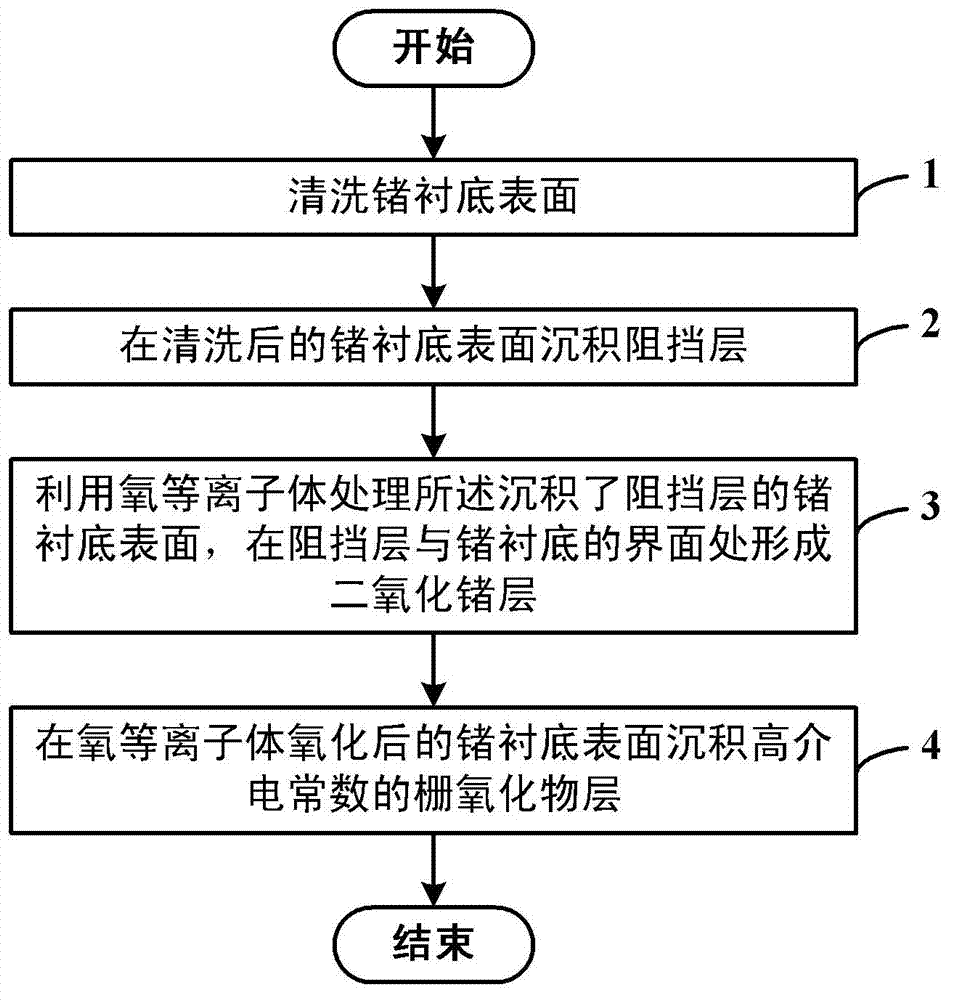

[0018] The method for preparing a germanium-based MOSFET gate dielectric provided by the present invention adopts lanthanum trioxide with a high dielectric constant as the plasma oxidation protection layer, and uses oxygen plasma to oxidize the surface of germanium to form a thin layer of germanium dioxide, thereby forming a high-quality The oxide-semiconductor interface, and finally depositing a high dielectric constant gate dielectric material on the surface of dilanthanum trioxide to form a composite gate dielectric of germanium dioxide-lanthanum trioxide-high dielectric constant gate dielectric material. The method can reduce the equivalent oxide layer thickness of the germanium-based MOSFET to less than 1 nanometer, t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More