Structure of perpendicular asymmetric ring gating metal oxide semiconductor field effect transistor (MOSFET) device and manufacturing method thereof

An asymmetric and device technology, applied in the formation of semiconductor devices, the structure and manufacture of vertical asymmetric gate-around MOSFET devices, can solve large junction leakage current, reduce channel carrier mobility, and insufficient gate control capability and other issues, to achieve the effect of enhancing gate control capability and superior device performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

[0033] combine figure 2 . As shown, an n-type silicon wafer substrate 101 with crystal orientation is prepared with a thickness of 100 nm.

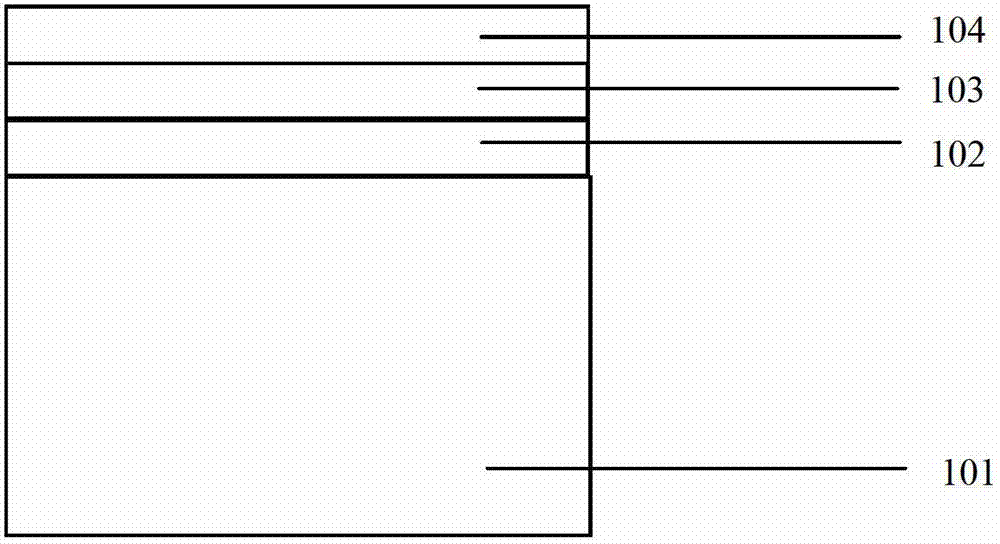

[0034] combine image 3 . On the n-type silicon wafer 101, SiO is sequentially deposited 2 layer 102, SiGe layer 103 and SiO 2 Layer 104. Of which SiO 2 layer 102, SiGe layer 103 and SiO 2 The thickness of the layer 104 is 20-50 nm.

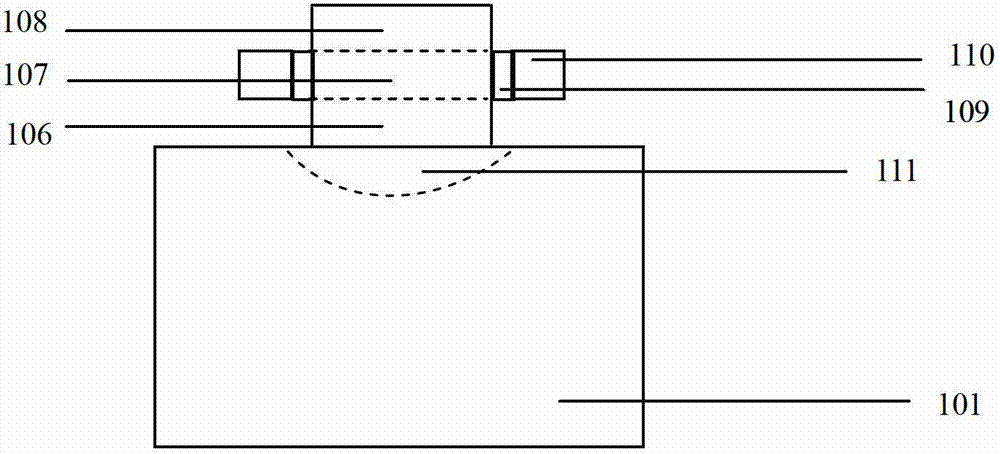

[0035] combine Figure 4 . right image 3 The structure is photolithographically made so that the middle part of the SiO 2 layer 102, SiGe layer 103 and SiO 2 Layer 104 is etched away in its entirety, forming a window. Then, the photoresist is used as a doping mask layer to perform n-type doping implantation on the silicon material, and rapid thermal annealing (RTA) activates the impurities to form the drain region 111 .

[0036] combine Figure 5 . The epitaxial silicon layer 105 is epitaxial on the silicon material, and the thickness of the epitaxial silicon layer 105 is 200-300nm. At the...

Embodiment 1

[0041] The advantages of Embodiment 1 are: 1) the gate-around structure is adopted, and the effective number of gates is the largest, so the gate has the strongest electrical control over the channel, and the short channel effect can be minimized; 2) the vertical channel is adopted Structure, no need to use complex lithography means to define the channel length, not limited by lithography accuracy, and the working principle and characteristics are almost the same as planar devices; 3) Using asymmetric LDD structure, compared with symmetric LDD structure, it can It has the advantages of reducing the cut-off leakage current, reducing the electric field near the drain junction, suppressing the short channel effect and reducing the series resistance of the source terminal. The manufacturing process is compatible with the planar CMOS process and is easy to implement; 4) Using the gate-last process, first perform self-aligned doping to form the source region, channel region and drain...

specific Embodiment 2

[0042] Other described steps are the same as the specific embodiment one.

[0043] combine Figure 7 . SiO 2 Layer 104 is a masking layer. Firstly, low-energy ion implantation is performed, the implantation energy is 20keV, and the dose is 5×10 13 cm -2 boron ions to form a graded channel; then perform high-energy ion implantation with an implantation energy of 20keV and a dose of 2×10 15 cm -2 of arsenic ions to form the source region. Rapid thermal annealing is then performed to activate the impurities. The doping concentration of the gradient channel region 107 gradually decreases from the source end to the drain end, which is 2×10 18 ~8×10 17 cm -3 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More