Preparation method of trench gate in trench MOS device

A technology of MOS devices and trench gates, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of easy concentration of electric field and affect the switching speed of trench-type MOS devices, etc., so as to reduce parasitic capacitance and reduce Switching loss, the effect of solving electrical breakdown

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

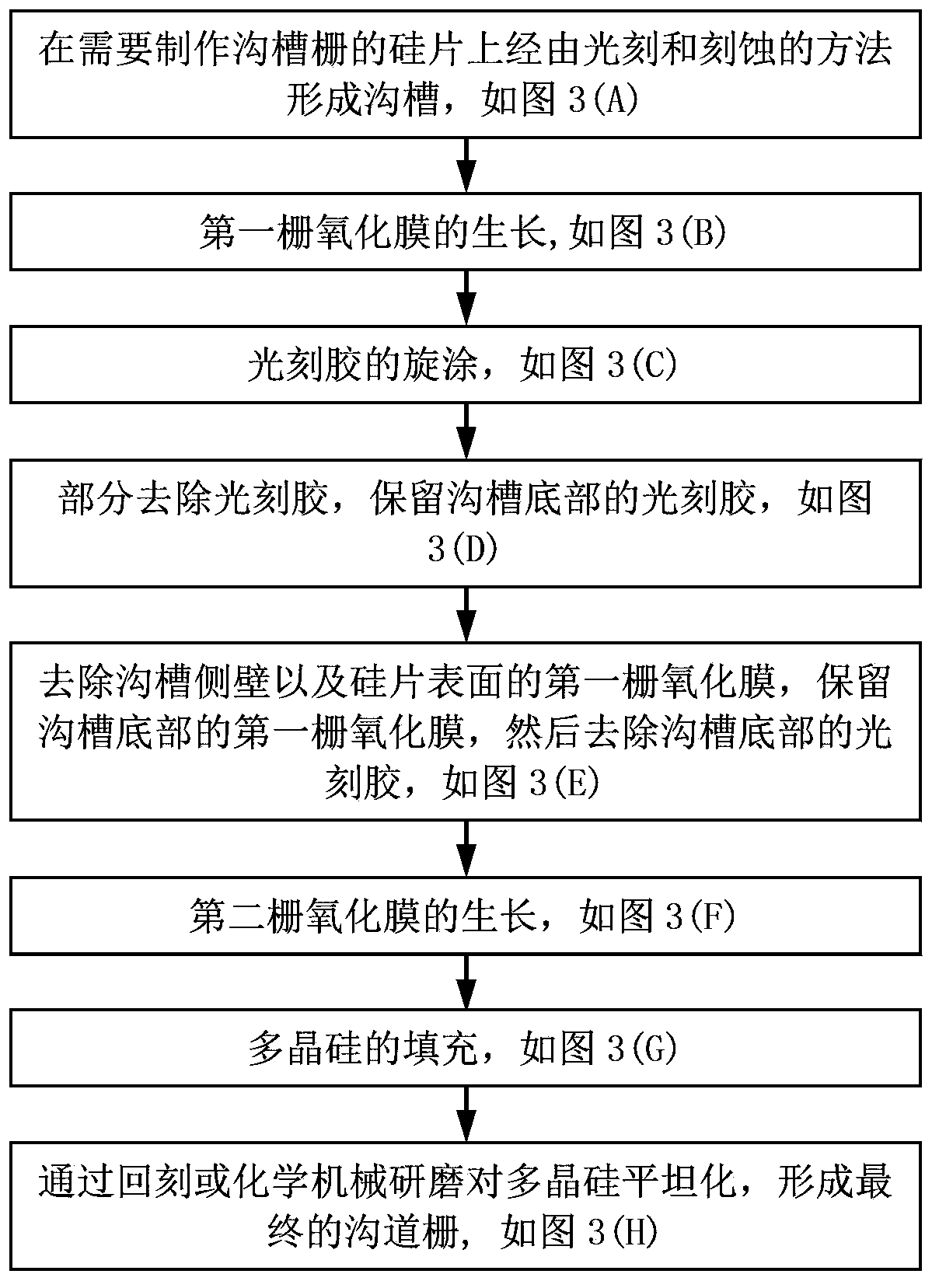

[0027] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments.

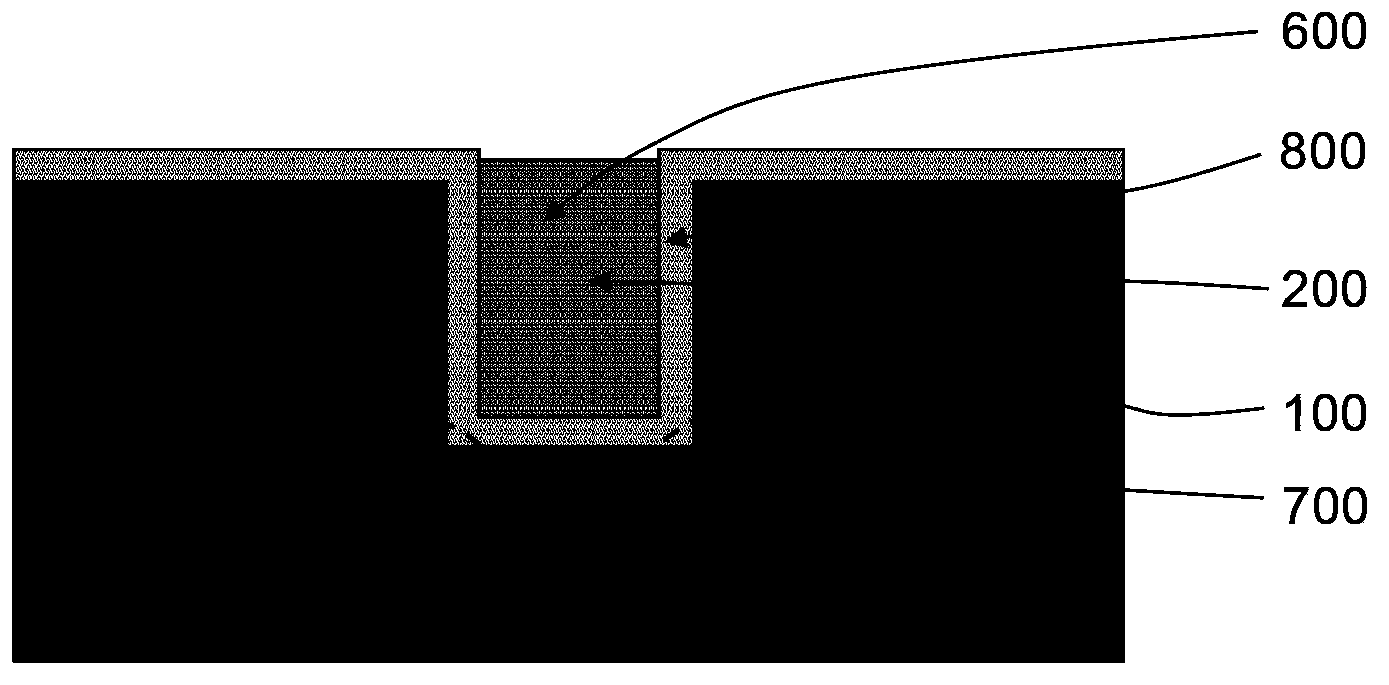

[0028] Such as figure 2 As shown in Fig. 3, the preparation method of trench gate in a kind of trench type MOS device of the present invention is characterized in that the gate oxide film at the bottom of the trench is thicker than the gate oxide film at the trench sidewall, comprising the following steps:

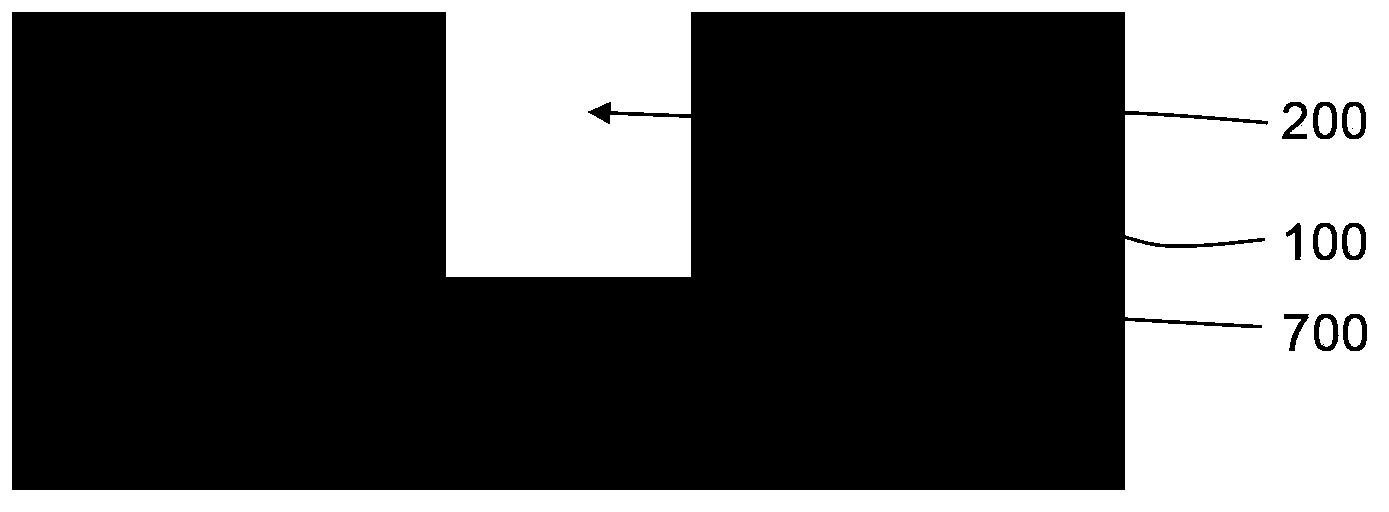

[0029] (1) As shown in Fig. 3 (A), on the silicon chip 100 that needs to make trench gate, form groove 200 through the method for photolithography and etching: described groove 200 is with photoresist pattern (in the figure not shown) is formed by etching a silicon wafer with a mask, or etching a silicon wafer with a dielectric film pattern (not shown in the figure) as a mask. Preferably, this embodiment uses a photoresist pattern as a mask, After dry etching the base silicon of the silicon wafer 100 and removing the photoresist, a trenc...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More