Gallium-nitride-based heterojunction field effect transistor with combined gate dielectric layer

A technology of heterojunction field effect and compound gate dielectric, which is applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve problems such as adverse effects on device electrical performance, threshold voltage drift, and subthreshold current increase, so as to reduce heat dissipation. Electronic effect, simple process and increased drift speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

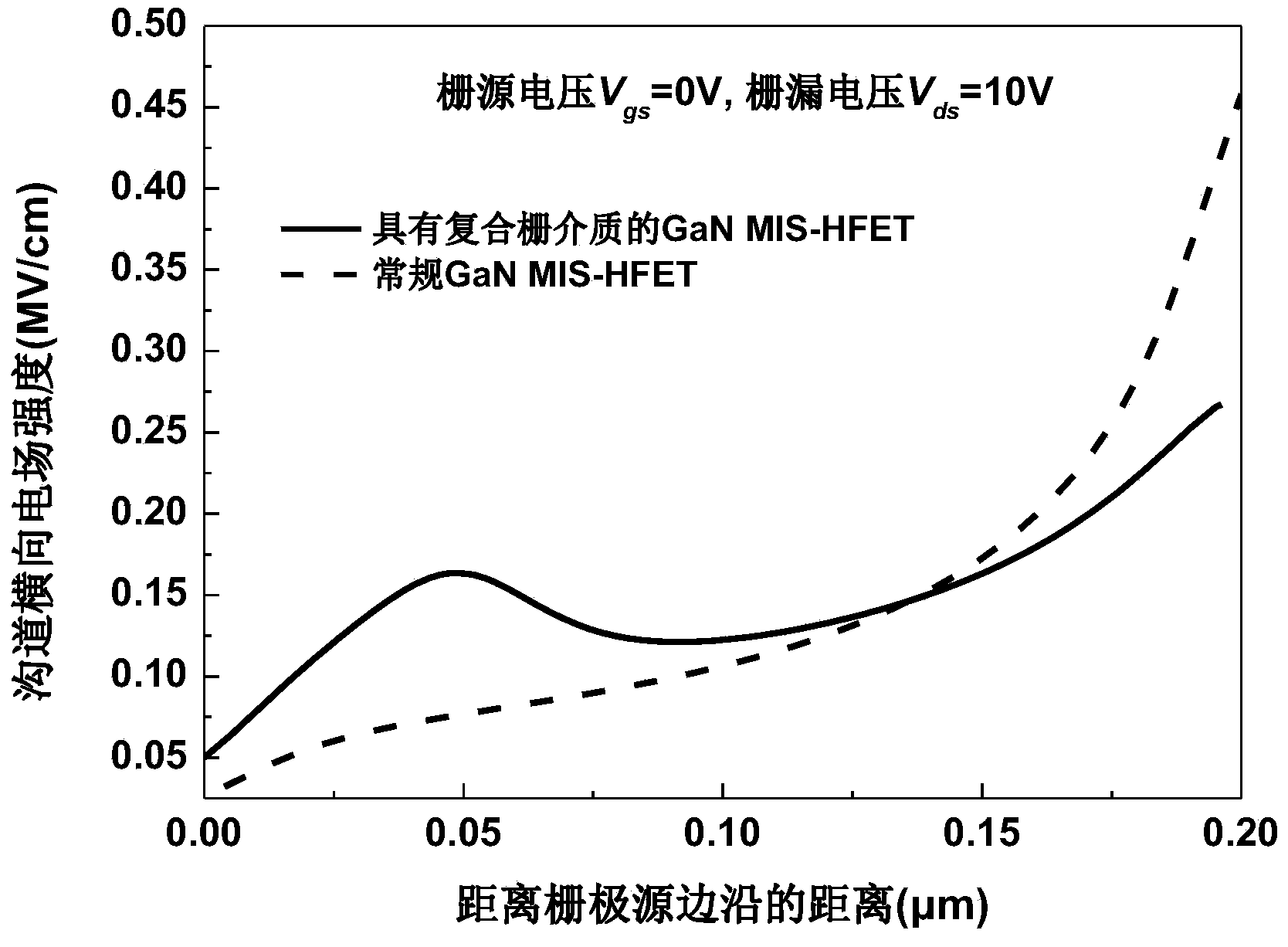

[0025] The easiest example to illustrate the purpose and advantages of the present invention to improve the frequency characteristics is provided by the present invention figure 2 The GaN MIS-HFET with the composite gate dielectric layer and the conventional structure GaN MIS-HFET ( figure 1 ) performance comparison; the structural parameters of the specific examples of the above two devices are given in Table 1.

[0026] Table 1 Microwave device simulation structure parameters

[0027]

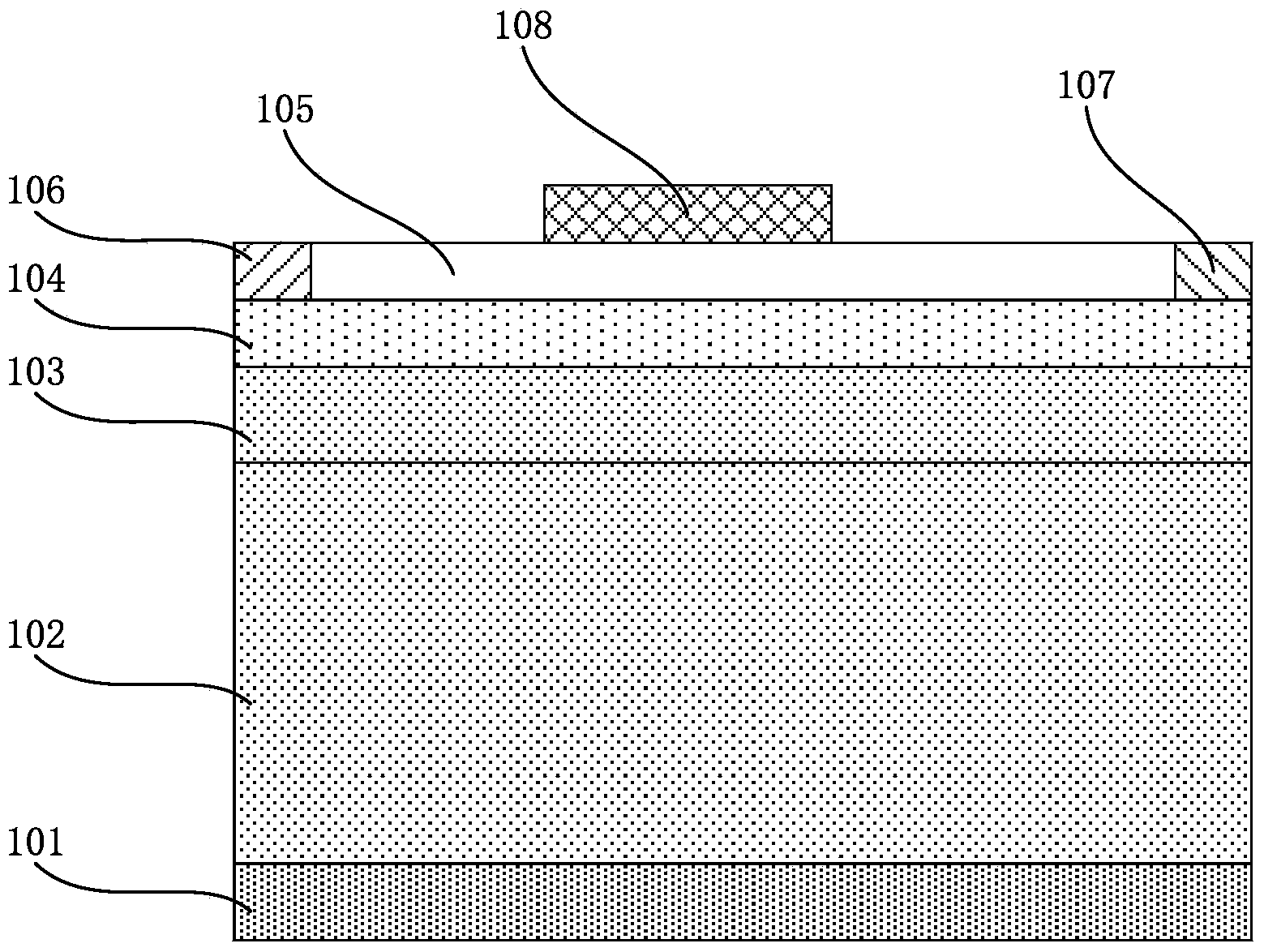

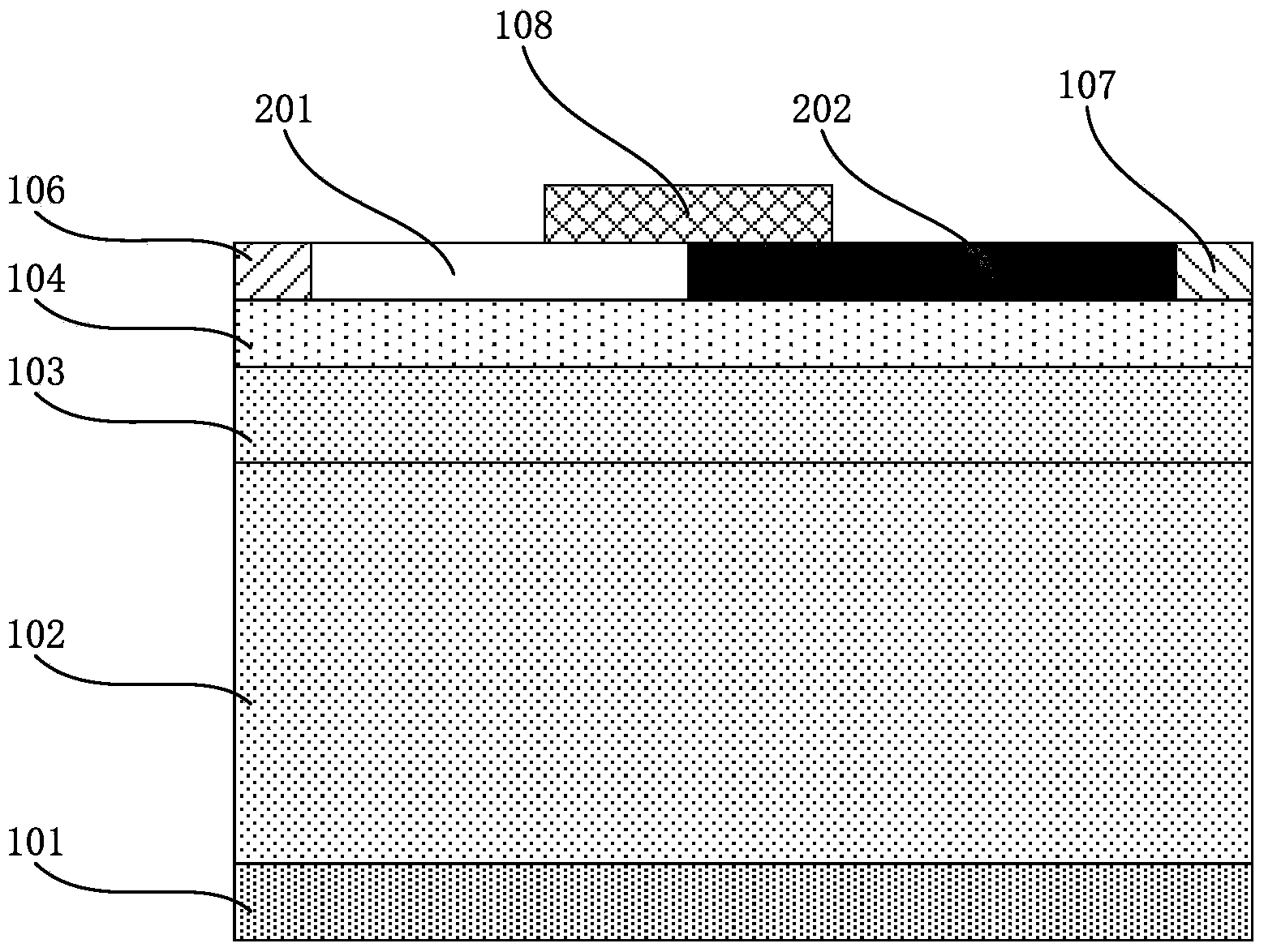

[0028] Provided based on the present invention such as image 3 In the GaN HEMT structure shown, the main process steps of the GaN HEMT provided in this embodiment are as follows: First, a gallium nitride buffer layer 102, a gallium nitride channel layer 103, and an aluminum gallium nitride layer are sequentially grown on a substrate 101 by MOCVD. (AlGaN) barrier layer 104, and then grow high dielectric constant dielectric layer 201 and low dielectric constant dielectric layer 202 respe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More