Method for improving open-circuit voltage of amorphous silicon tandem solar cell

A solar cell and open-circuit voltage technology, applied in circuits, photovoltaic power generation, electrical components, etc., can solve the problem of insignificant increase in Voc

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

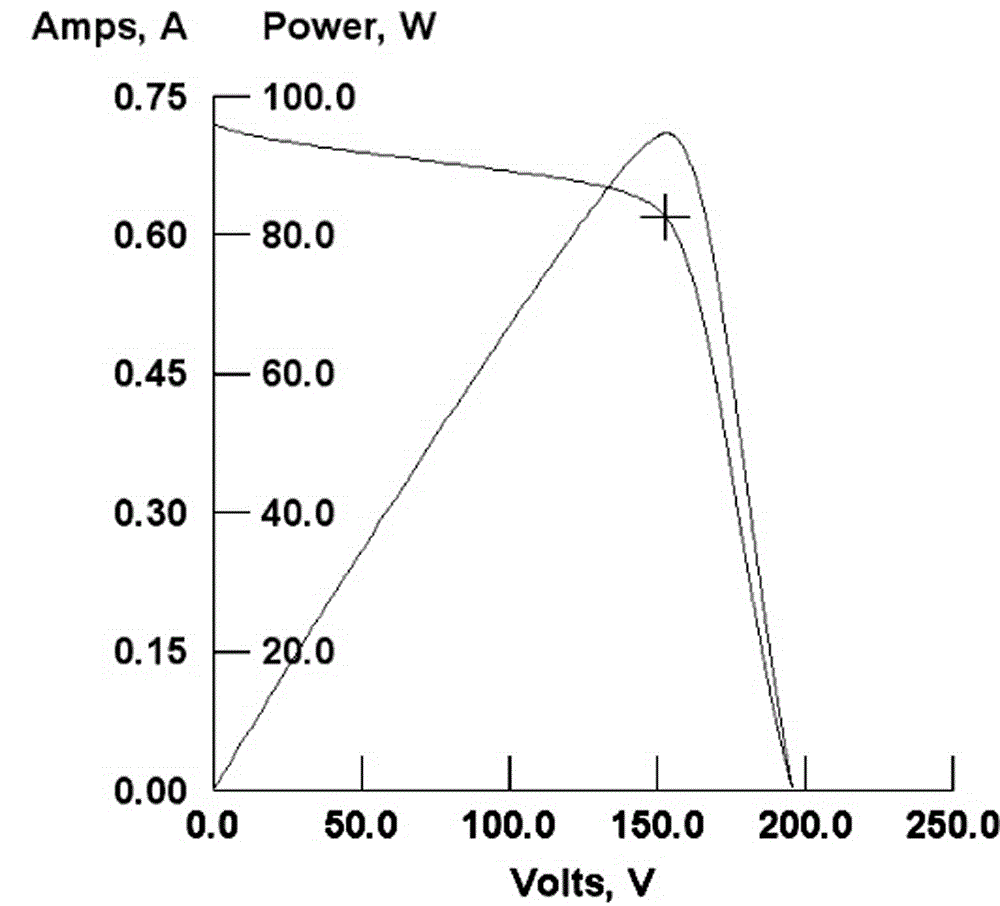

Embodiment 1( comparative Embodiment )

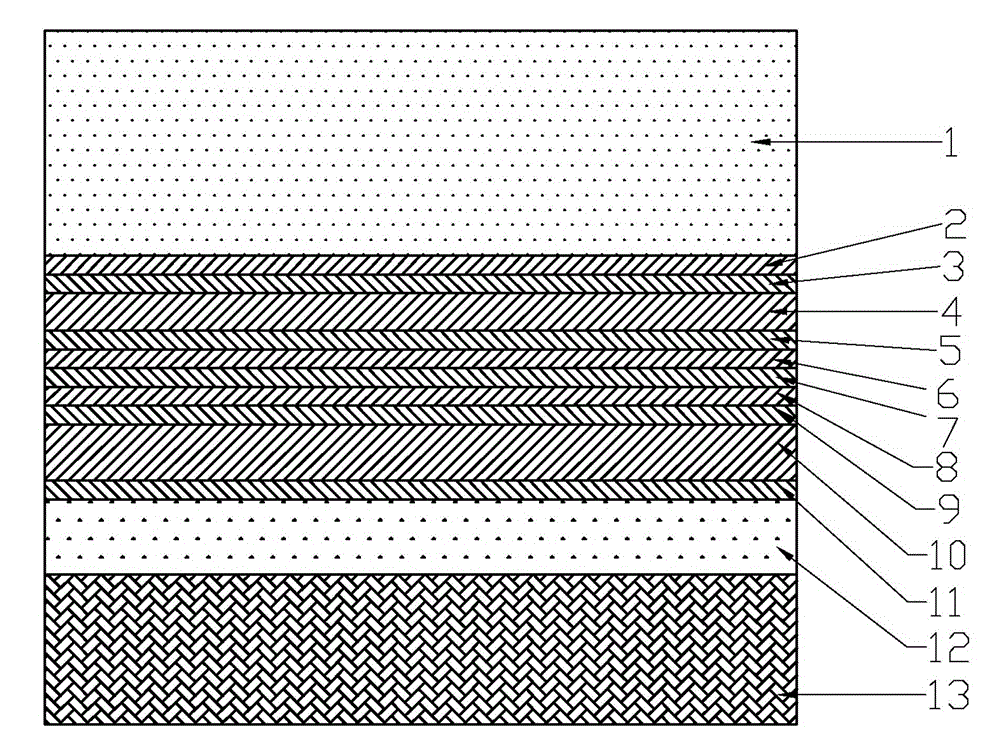

[0053] 1) With a transparent conductive glass (F-SnO2) with a tin oxide film thickness of 700nm as the substrate, a 10nm top-cell amorphous silicon P-type layer and a 10nm top-cell amorphous silicon P-type layer were sequentially deposited by 13.56MHz plasma chemical vapor deposition Buffer layer, 50nm top cell amorphous silicon I layer, 10nm top cell microcrystalline silicon N-type layer, 3nm bottom cell amorphous silicon P1 layer, 10nm bottom cell amorphous silicon P2 layer, 10nm amorphous silicon buffer Layer, 150nm bottom cell amorphous silicon I layer, 10nm bottom cell amorphous silicon N-type layer;

[0054] Among them, when depositing the microcrystalline silicon N-type layer of the top cell, the flow rate of phosphine is 200 sccm, the flow rate of hydrogen gas is 10 slm, and the flow rate of silane is 400 sccm; the deposition pressure of the microcrystalline N-type layer is 220 Pa, and the deposition power is 1.3 kW. When depositing the bottom cell amorphous silicon P1...

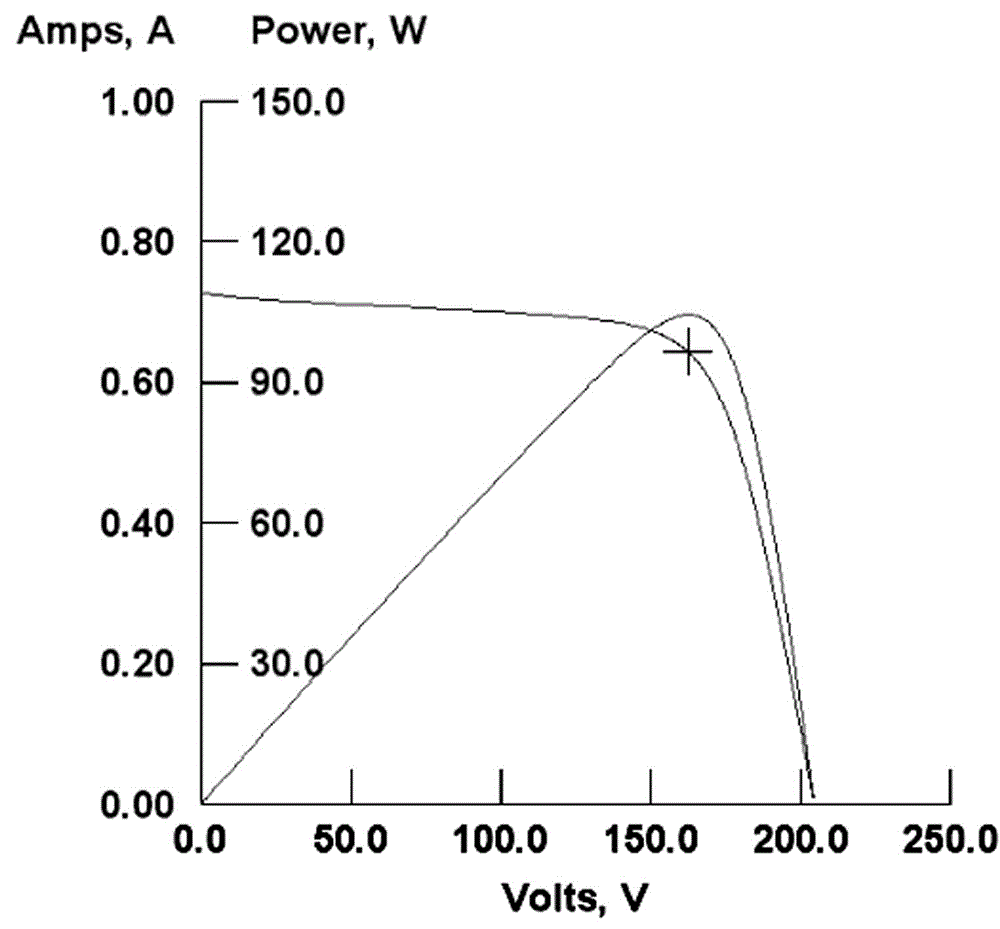

Embodiment 2

[0059] 1) Use transparent conductive glass (F-SnO2) with a tin oxide film thickness of 700nm as the substrate 1, and use 13.56MHZ plasma chemical vapor deposition to sequentially deposit a 10nm top cell amorphous silicon P-type layer, and a 10nm top cell amorphous silicon layer. Silicon buffer layer, 50nm top cell amorphous silicon I layer, 10nm top cell microcrystalline silicon N-type layer, 3nm bottom cell amorphous silicon P1 layer, 3nm bottom cell amorphous silicon P2 layer, 10nm bottom cell non-crystalline silicon Crystalline silicon P3 layer, 10nm amorphous silicon buffer layer, 150nm bottom cell amorphous silicon I layer, 10nm bottom cell amorphous silicon N-type layer;

[0060] Wherein, when depositing the microcrystalline silicon N-type layer 5 of the top cell, the pH 3 (phosphine) flow is 200sccm, H 2 (Hydrogen) with a flow rate of 10slm, SiH 4 The flow rate of (silane) is 400 sccm; the deposition pressure of the microcrystalline N-type layer is 220 Pa, and the dep...

Embodiment 3

[0065] 1) Use transparent conductive glass (F-SnO2) with a tin oxide film thickness of 700nm as the substrate 1, and use 13.56MHZ plasma chemical vapor deposition to sequentially deposit a 10nm amorphous silicon P-type layer for the top cell, and a 10nm amorphous silicon layer for the top cell Silicon buffer layer, 50nm top cell amorphous silicon I layer, 10nm top cell microcrystalline silicon N-type layer, 3nm bottom cell amorphous silicon P1 layer, 3nm bottom cell amorphous silicon P2 layer, 10nm bottom cell non-crystalline silicon Crystalline silicon P3 layer, 10nm amorphous silicon buffer layer, 150nm bottom cell amorphous silicon I layer, 10nm bottom cell amorphous silicon N-type layer;

[0066] Among them, when depositing the microcrystalline silicon N-type layer 5 of the top cell, the flow rate of phosphine is 200 sccm, the flow rate of hydrogen gas is 10 slm, and the flow rate of silane is 400 sccm; the deposition pressure of the microcrystalline N-type layer is 220 Pa,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More