Manufacturing technology for transistor

A preparation process and transistor technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as limited technical effect, long crystallization time, and large grain roughness, so as to enhance flexibility and reduce Effects of roughness, process flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0033] The invention provides a transistor preparation process, specifically a low-leakage thin-film transistor low-temperature polysilicon preparation process. In any process after the deposition of amorphous silicon and before S / D heavy doping, the wavelength is 320nm~ The 550nm laser is irradiated from the side of the substrate 1 to melt and crystallize the amorphous silicon to form polysilicon, and then replace the conventional step of using a laser source to irradiate from the side of the substrate 1 with the film. And the present invention uses a laser source with a wavelength of 320nm~550nm instead of a 308nm laser source in the conventional preparation process.

[0034] The invention provides a preparation process of a transistor, comprising the following steps:

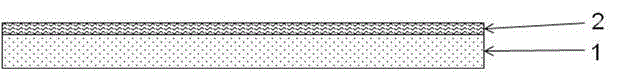

[0035] Step 1: If figure 1 As shown, the substrate 1 is selected, and a single-layer or double-layer buffer layer 2 is deposited on the substrate 1; then a layer of amorphous silicon layer 3 is deposited on ...

Embodiment 1

[0049] This embodiment provides a fabrication process for a transistor, including the following steps:

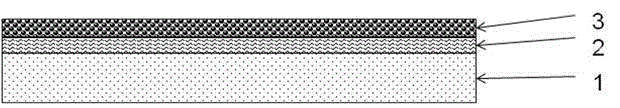

[0050] Step 1: If figure 1 As shown, the substrate 1 is selected, and a single-layer buffer layer 2 is deposited on the substrate 1; then a layer of amorphous silicon layer 3 is deposited on the buffer layer 2, and the amorphous silicon layer 3 is lightly doped amorphous silicon, such as figure 2 As shown, a-Si deposition is completed.

[0051] The substrate 1 may be a quartz substrate that transmits a laser wavelength of 320nm.

[0052] The material of the buffer layer 2 is Si 3 N 4 , with a thickness of 500nm. S

[0053] The thickness of the amorphous silicon layer 3 is 10nm, and the third main group is doped in the amorphous silicon layer 3, and its doping concentration is 1E10cm -2 , to increase the mobility of the amorphous silicon layer 3 .

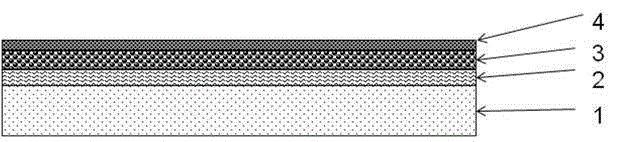

[0054] Step 2: If image 3 As shown, an insulating layer 4 with a thickness of 50 nm is deposited on the amorphous sil...

Embodiment 2

[0063] This embodiment provides a fabrication process for a transistor, including the following steps:

[0064] Step 1: If figure 1 As shown, the substrate 1 is selected, and a double-layer buffer layer 2 is deposited on the substrate 1; then a layer of amorphous silicon layer 3 is deposited on the buffer layer 2, and the amorphous silicon layer 3 is lightly doped amorphous silicon, such as figure 2 As shown, a-Si deposition is completed.

[0065] The substrate 1 may be an acrylic substrate that transmits 550nm laser light.

[0066] The material of the buffer layer 2 is SiO 2 , with a thickness of 300nm.

[0067] The thickness of the amorphous silicon layer 3 is 500nm, and the amorphous silicon layer 3 is doped with elements of the fifth main group (such as boron, phosphorus or arsenic) with a doping concentration of 1E12cm -2 , to increase the mobility of the amorphous silicon layer 3 .

[0068] Step 2: If Figure 4 As shown, a laser with a wavelength of 550nm is irrad...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| wavelength | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com