High-voltage semiconductor device and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of large electric field on the surface of the device, high requirements for process control, and high requirements for process equipment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

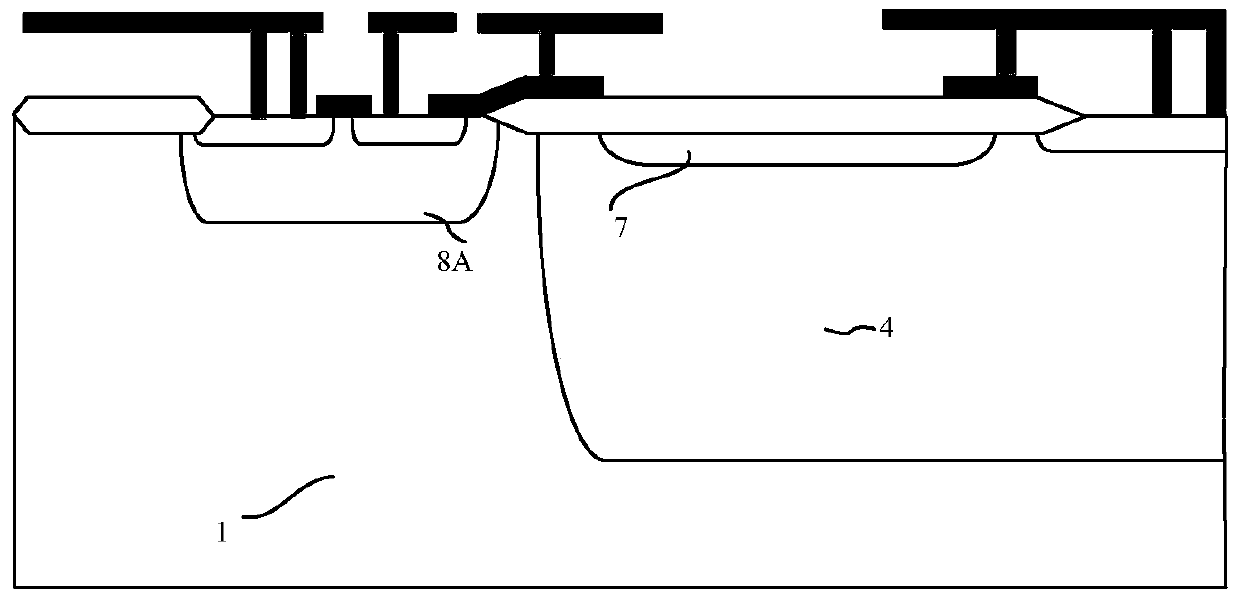

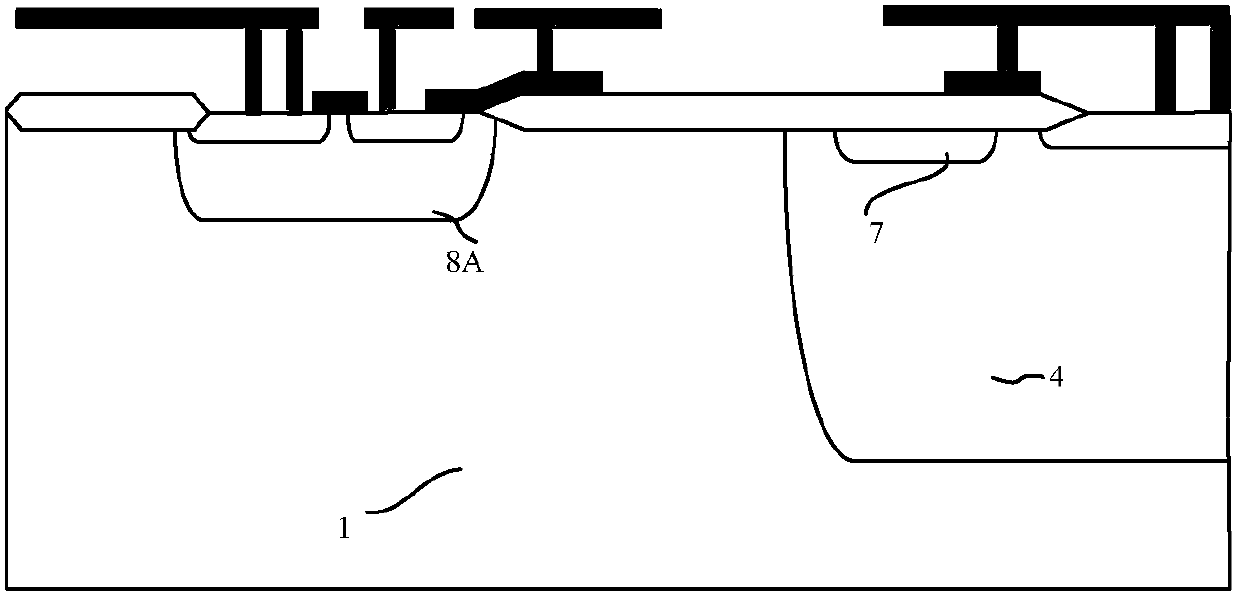

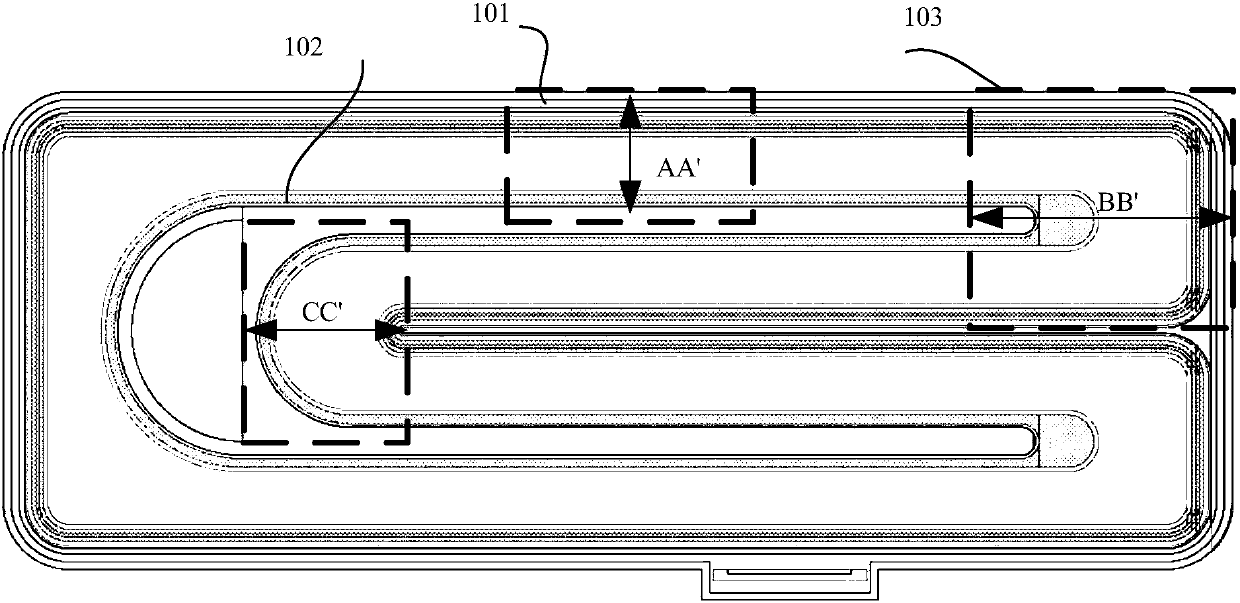

[0124] refer to figure 2 , figure 2 The complete layout of the semiconductor device according to the first embodiment is shown, and the device layout of this embodiment is an interdigitated layout to obtain sufficient current capability. The layout mainly includes a straight edge portion 101 , a source fingertip portion 102 , a drain fingertip portion 103 and other portions. In different regions of the layout, the cross-sectional structure of the device is not exactly the same. Among them, the straight edge part 101 is arranged along a straight line and is the main conductive part of the device; the drain finger tip part 103 and the source finger tip part 102 can be collectively referred to as the chamfered part. Along a single straight line, it has an arc or corner area. The main function of the chamfered part is to provide the transition of the complete device layout and ensure the effective withstand voltage of the device.

[0125] refer to image 3 , image 3 for ...

no. 2 example

[0139] In the second embodiment, the formation process of the buried layer will be described in detail.

[0140] refer to Figure 5A and Figure 5B , which shows the formation process of the buried layer 2 of a nonlinear variable doping structure. Such as Figure 5A As shown, ion implantation is performed using a mask 20 as a mask, wherein the mask 20 may be patterned photoresist or other suitable mask materials. After the ion implantation, the edge portion of the buried layer 2 can be expanded laterally by high-temperature pushing junction, so as to obtain the buried layer 2 with a nonlinear graded doping structure. Figure 5B Shown is a topography diagram of the buried layer 2 after ion implantation and annealing, wherein the buried layer 2 is a single doped region.

[0141] refer to Figure 6A and Figure 6B , which shows a formation process of the buried layer 2 adopting a linear variable doping structure. Figure 6A As shown, ion implantation is performed using a m...

no. 3 example

[0144] refer to Figure 8 , Figure 8 A schematic cross-sectional structure diagram of a straight-side portion of the high-voltage semiconductor device of the third embodiment is shown. figure 2 The straight edge part 101 in can be obtained by cutting along AA' Figure 8 The sectional view shown. Figure 8 The structure shown and image 3 The structures shown are basically the same, except that the P-type doped buried layer 2 adopts a linearly variable doping structure, including a plurality of mutually separated doping regions. The advantage of this is: without increasing the complexity of the process, only slight changes are made on the layout, so that the buried layer 2 forms a linear variable doping structure, thereby optimizing the electric field distribution at the source end, improving the reliability of the device, and The linearly variable doping processes of the source fingertip parts are matched to each other.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More