Integration method of vertical nanowire device of air side wall structure

An air-side, nanowire technology, applied in the manufacture of electrical components, semiconductor devices, semiconductor/solid-state devices, etc., can solve the problems of difficult to control the channel cross-sectional morphology, degradation of device characteristics consistency, affecting the high-frequency characteristics of devices, etc. Achieve the effect of reducing penetration, reducing the degradation of on-state current, and improving frequency characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0089] The present invention will be described in detail below in conjunction with the accompanying drawings and specific examples.

[0090] A vertical nanowire NMOSFET with an air sidewall structure on an SOI substrate can be realized according to the following steps:

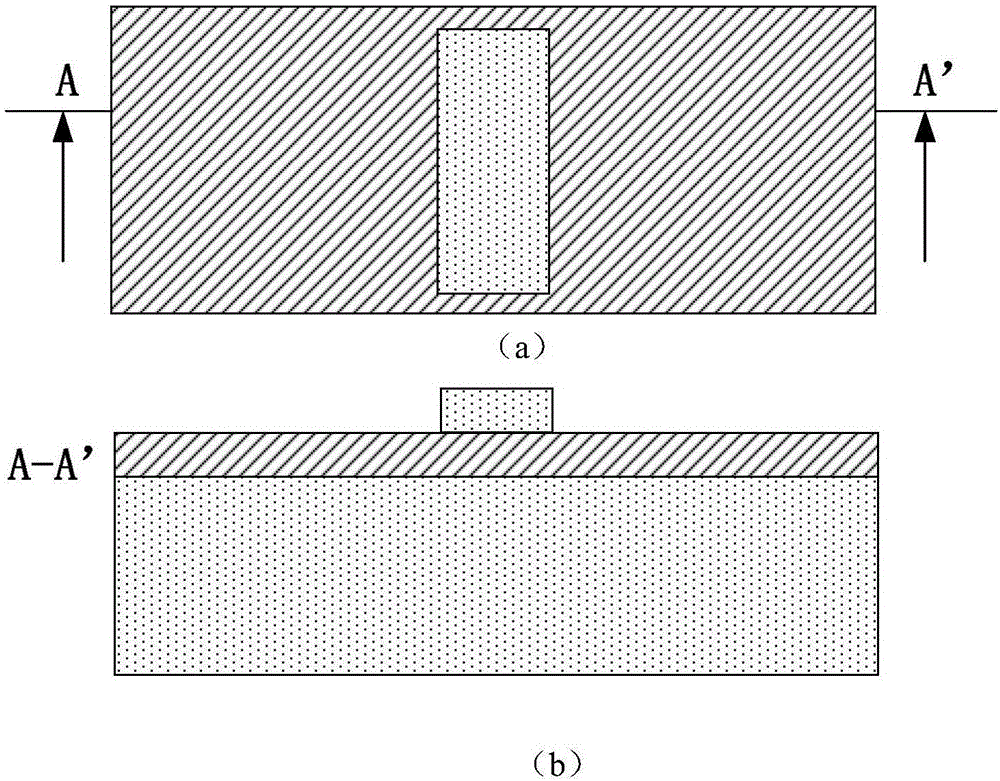

[0091] 1) On the (100) P-type lightly doped SOI substrate, use HNA solution to thin the top silicon film to 20nm, define the lower active region of the device by photolithography and RIE etching, and remove the glue, such as figure 1 shown;

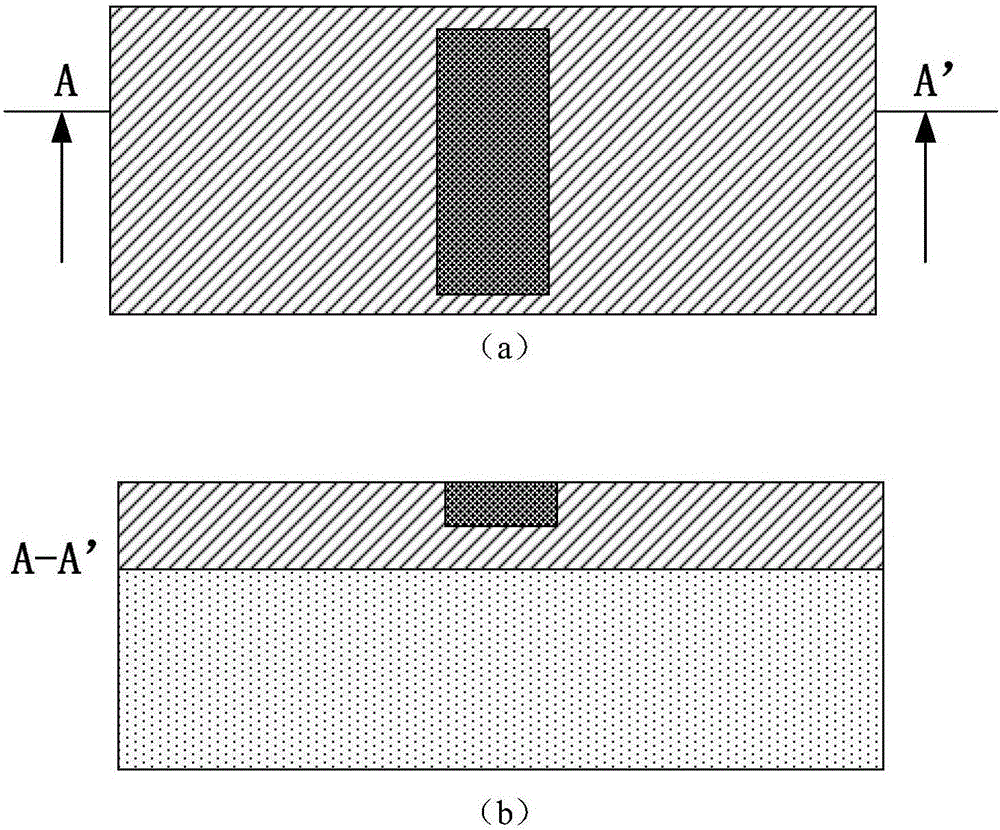

[0092] 2) Perform As + Implant doping to form the lower active region of the device (as the source end of the device), the implantation energy is 10KeV, and the implantation dose is 5E15cm -2 ;

[0093] 3) LPCVD SiO 2 40nm, the surface is planarized by chemical mechanical polishing, exposing the upper surface of the active region under heavy doping, forming STI, such as figure 2 shown;

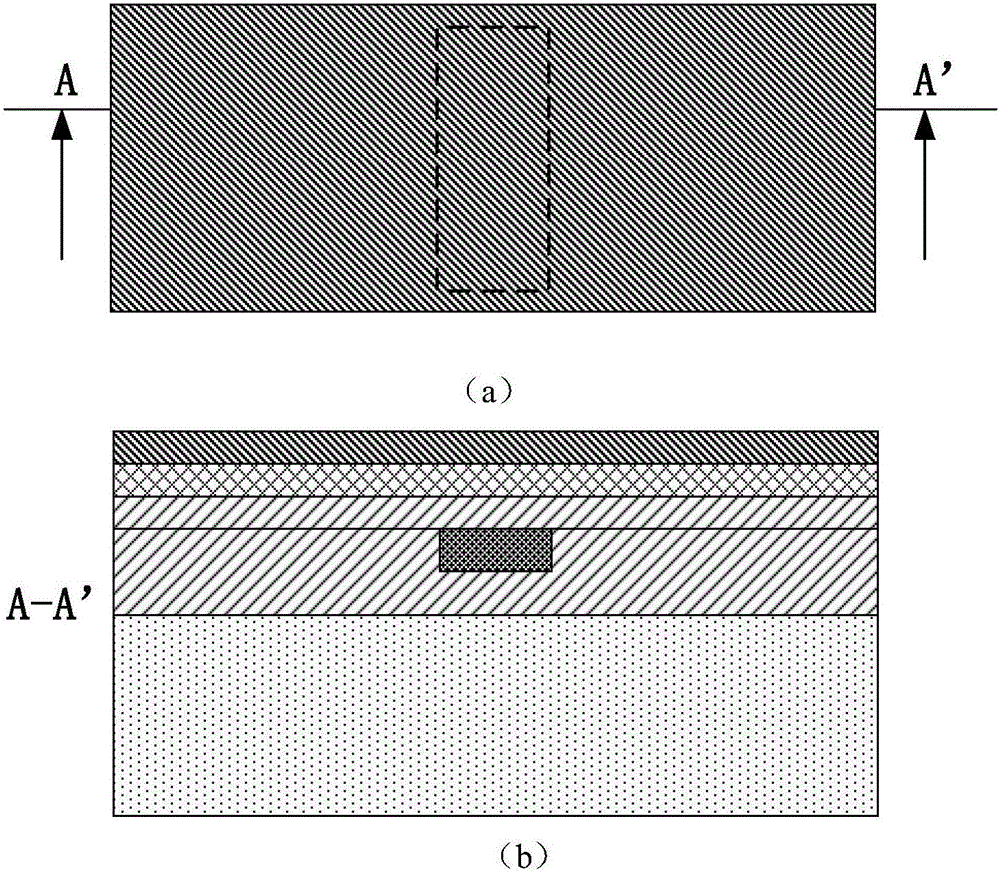

[0094] 4) Deposit 10nm SiO sequentially by ALD 2 (as the SDE mask layer 1, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com