Mixed light interconnection system based on standard CMOS (Complementary Metal-Oxide-Semiconductor Transistor) process

An interconnection system and mixed light technology, which is applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve the problems of weak detection performance of Si-based LEDs and inability to realize two-way communication, so as to reduce light transmission distance, reduce electrical interference, and avoid The effect of crosstalk

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

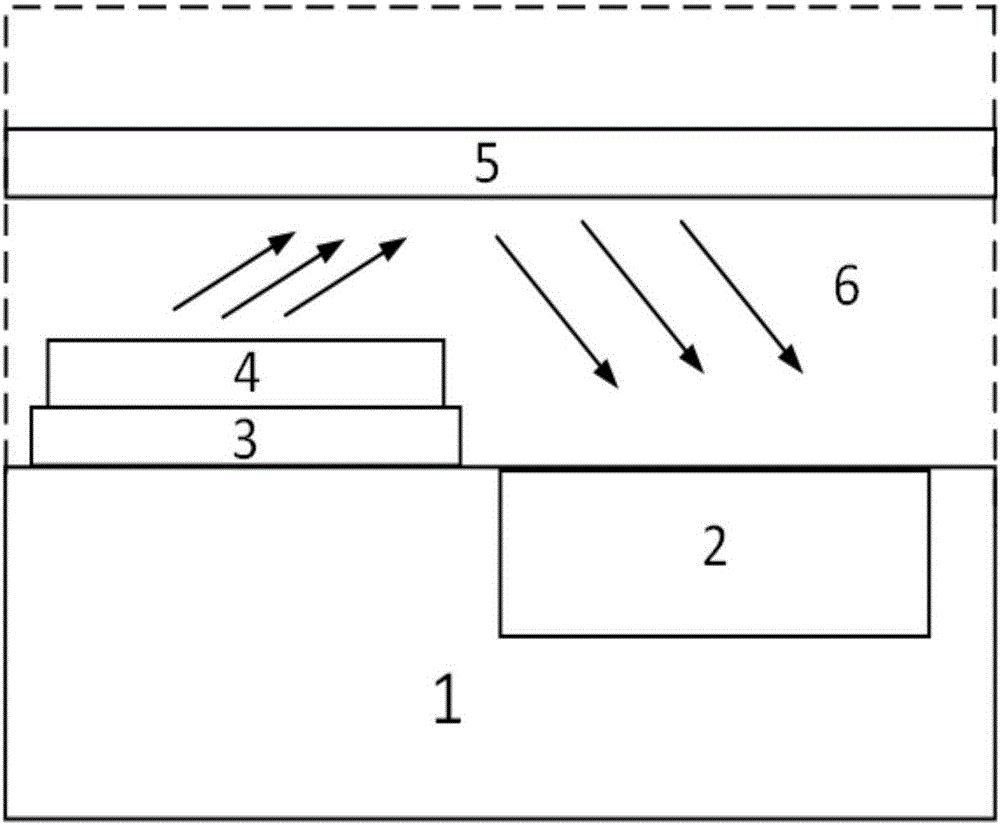

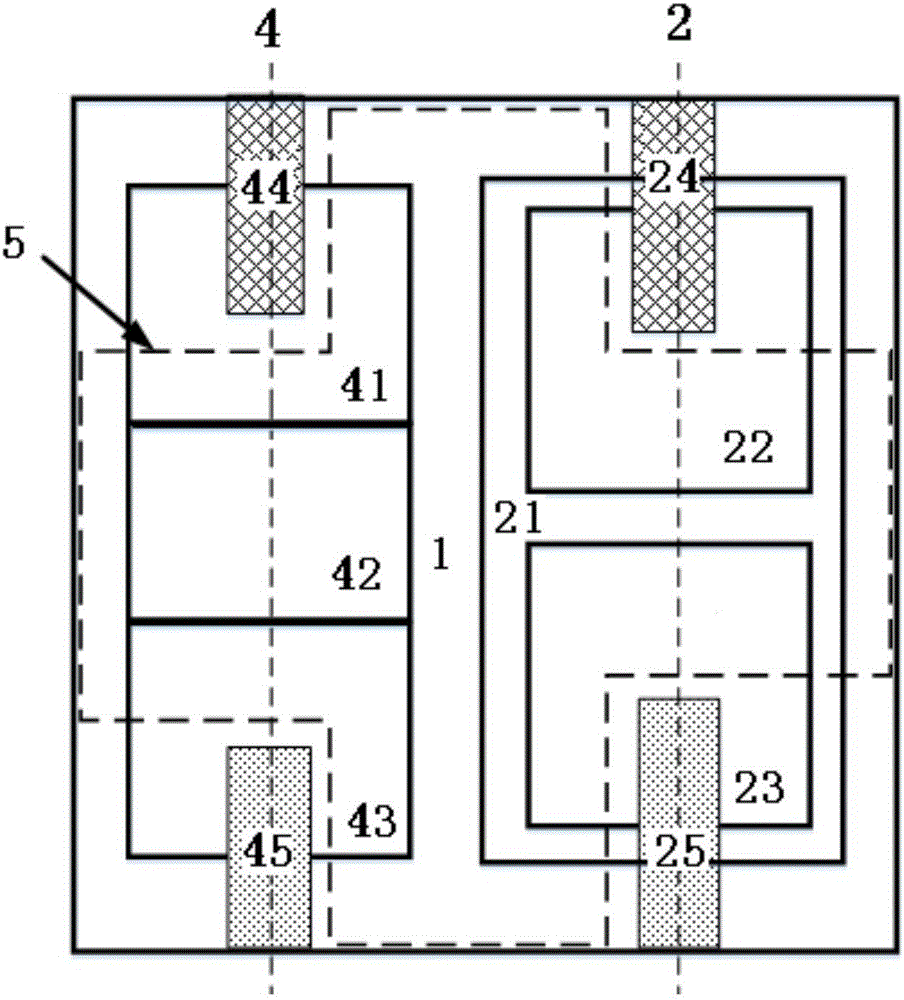

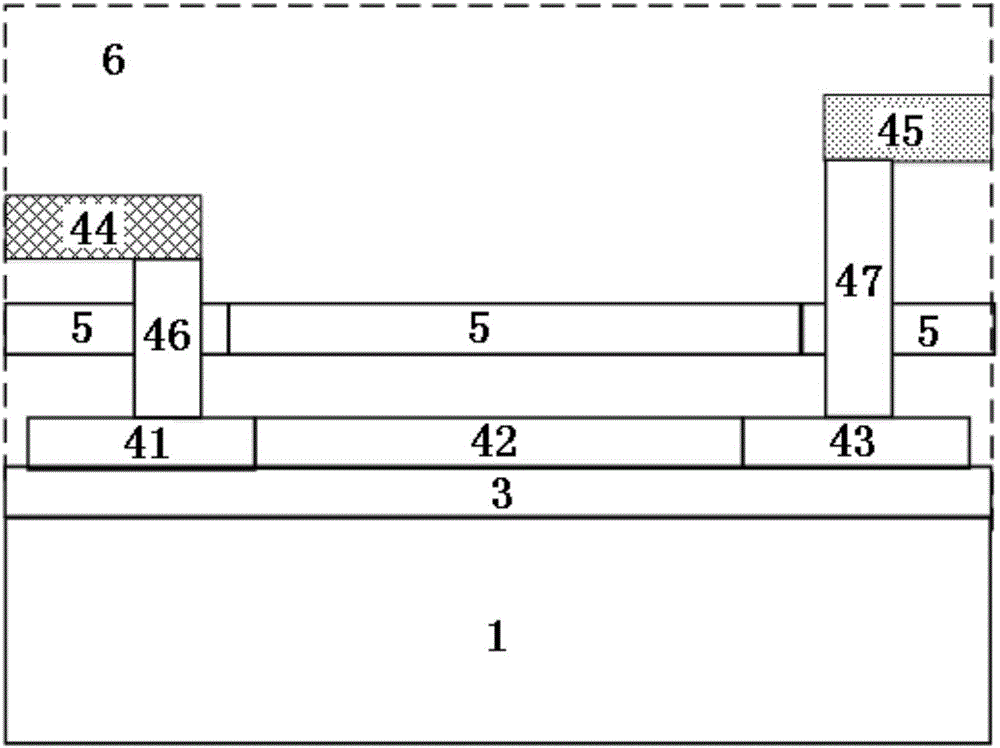

[0028] A hybrid optical interconnection system based on a standard CMOS process of the present invention will be described in detail below with reference to embodiments and drawings.

[0029] A hybrid optical interconnection system based on a standard CMOS process of the present invention includes a polysilicon LED, an optical waveguide, a single crystal silicon detector composed of a P+ / N well, and a P-type substrate; the polysilicon LED includes a polysilicon LED anode and its The contact area, the polysilicon LED cathode and its contact area, and the i area of the polysilicon LED; the polysilicon LED can emit infrared light with forward bias, and can also emit visible light with reverse bias. The waveguide is metal and its underlying SiO 2 layer; the monocrystalline silicon photodetector includes a monocrystalline silicon detector anode and its contact, a monocrystalline silicon detector cathode and its contact, and an N well in a P-type substrate; the photodetector is re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More