Manufacturing method of fan-out chip interconnection

A manufacturing method and fan-out technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems of reducing the area of functional parts, poor reliability, and large occupied area, so as to increase reliability, The effect of reducing the difficulty of interconnection and reducing the problem of open circuit and short circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0037] A method for fabricating fan-out chip interconnection, comprising:

[0038] A: Rewire the surface of the fan-out chip and introduce the PAD to the chip surface;

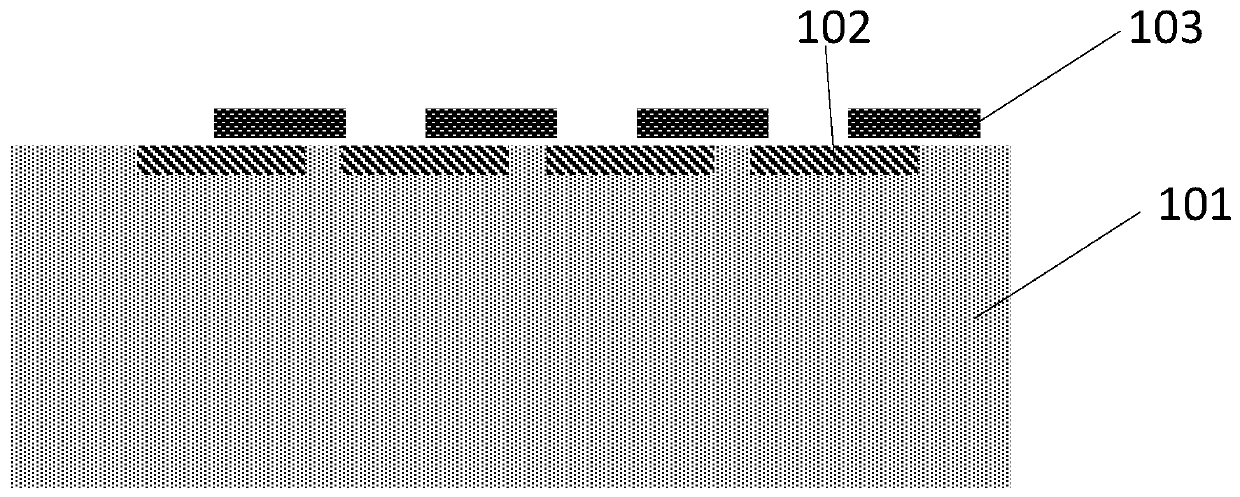

[0039] Such as figure 1 As shown, the chip 101 that needs to be embedded in the groove of the silicon interposer is coated with a photoresist or a passivation layer 103 on the surface. The photoresist can be positive or negative, with a thickness ranging from 1um to 100um. The oxide layer can be silicon oxide or silicon nitride with a thickness ranging from 10nm to 100um;

[0040] If it is photoresist, the PAD area 102 needs to be opened by an exposure process to expose the chip PAD;

[0041] If it is a passivation layer, the passivation layer in the PAD area needs to be removed by photolithography and etching;

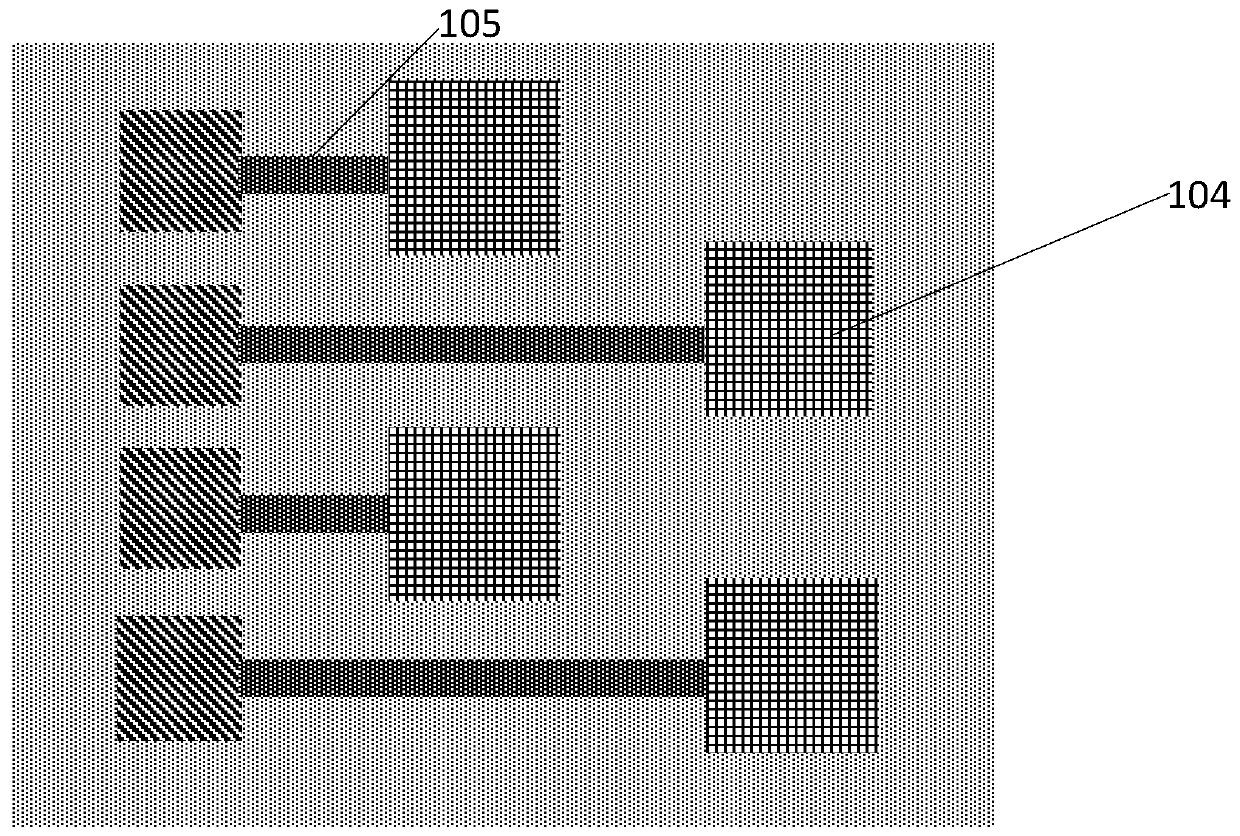

[0042] Then make the RDL interconnection circuit 105 on the chip surface, first make a seed layer on the insulating layer by physical sputtering, magnetron sputtering or evaporation process, the th...

Embodiment 2

[0050] A method for fabricating fan-out chip interconnection, comprising:

[0051]A: Cover the PAD on the surface of the fan-out chip with a passivation layer, and make a photoresist on the surface of the passivation layer;

[0052] Such as figure 1 As shown, the chip that needs to be embedded in the groove of the silicon interposer is coated with photoresist or passivation layer on the surface. The photoresist can be positive or negative, and the thickness ranges from 1um to 100um. The passivation layer It can be silicon oxide or silicon nitride with a thickness ranging from 10nm to 100um;

[0053] B: Perform photolithography and etching on the chip PAD to reduce the exposed interconnected metal area on the surface of the PAD;

[0054] If it is photoresist, it is necessary to use the exposure process to open the PAD area to expose the chip PAD;

[0055] If it is a passivation layer, the passivation layer in the PAD area needs to be removed by photolithography and etching; ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More