Method for realizing hole local passivation contact, and crystalline silicon solar cell and preparation method thereof

A crystalline silicon, local technology, applied in the field of solar cell preparation, can solve the problems of difficult application of local passivation contact structure, cumbersome preparation steps, cumbersome process steps, etc., and achieves less photogenerated carrier transmission loss, simple process, high photogenerated Effect of carrier collection probability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 3

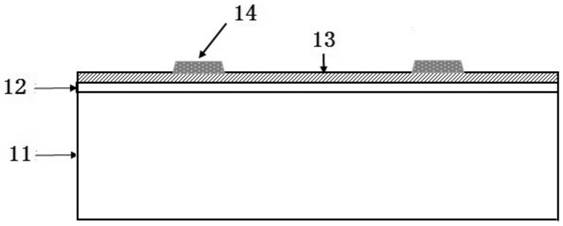

[0072] Embodiment 3 discloses a solar cell structure with a hole local passivation contact structure and a preparation method thereof. The battery structure given in this embodiment is as follows image 3 As shown, the front side of the battery adopts hole-local passivation contacts, and the back side of the battery adopts full-area electron passivation contacts. The substrate material here is n-type single crystal silicon (or p-type single crystal silicon).

[0073] The preparation method of the battery is as follows:

[0074] A1: Select a 156mm*156mm (100) n-type monocrystalline silicon wafer with a resistivity of 1 Ω·cm and a thickness of 180 μm.

[0075] A2: NaOH polishing is used to remove the damaged layer (about 10 μm) on the surface of the n-type silicon wafer.

[0076]A3: A tunneling silicon oxide layer is prepared on both sides of the n-type silicon wafer by a thermal oxidation process, with a thickness of 1.5 nm and a refractive index of 1.46.

[0077] A4: Intri...

Embodiment 4

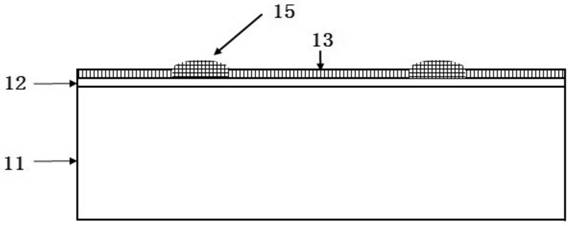

[0087] Embodiment 4 discloses another solar cell structure with a hole-local passivation contact structure and its preparation method. The battery structure given in this embodiment is as follows Figure 4 As shown, the front side of the battery adopts hole local passivation contact, and the back side of the battery adopts n-type doped junction and corresponding passivation film. In this example, the substrate material is p-type single crystal silicon. The battery preparation method is as follows:

[0088] B1: Choose a p-type monocrystalline silicon wafer with a (100) crystal orientation of 156mm*156mm, a resistivity of 1 Ω·cm, and a thickness of 180 μm.

[0089] B2: Polishing with sodium hydroxide solution to remove the damaged layer (about 10 μm) on the surface of the p-type silicon wafer.

[0090] B3: A tunneling silicon oxide layer is prepared on the surface of the p-type silicon wafer by a thermal oxidation process, with a thickness of 1.3 nm and a refractive index of ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More