Manufacturing method of super junction device

A manufacturing method and super junction technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of gate dielectric layer damage, inability to form a protective effect, and inability to prevent polysilicon gate impurities from accumulating on the silicon surface, etc. To achieve the effect of preventing the external expansion of doping impurities and preventing damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

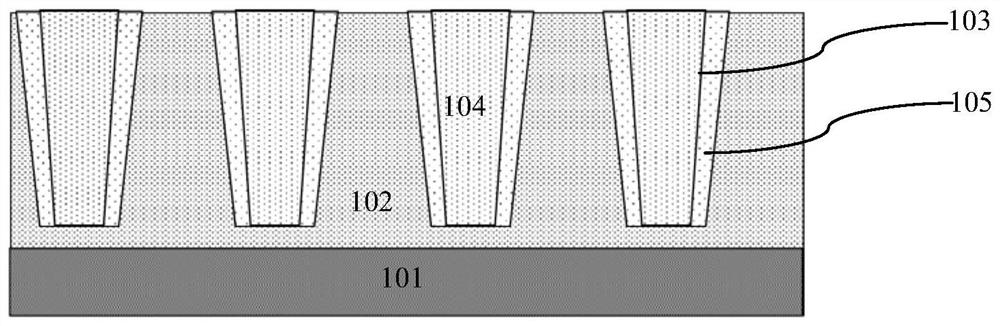

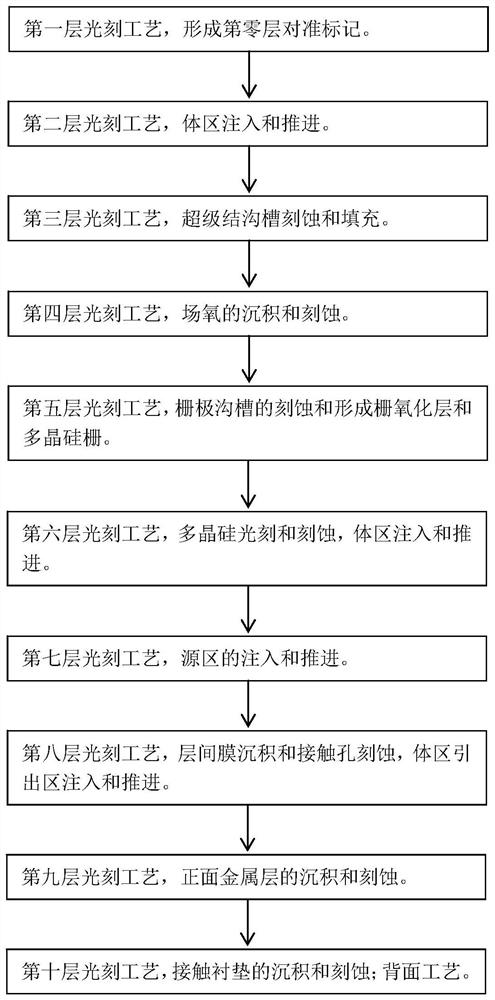

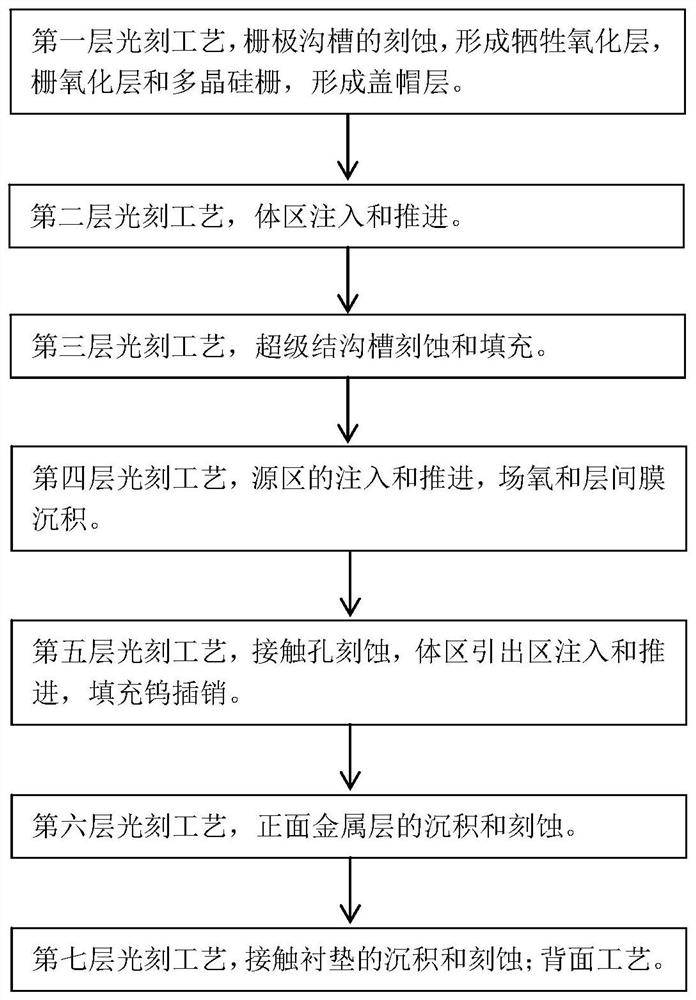

[0089] Such as image 3 Shown is a flowchart of a method for manufacturing a super junction device according to an embodiment of the present invention; image 3 It is described according to the lithography process level. A lithography process level includes multiple specific process steps. In a lithography process level, only the lithography process corresponding to one mask is performed; for example Figure 4A to Figure 4N As shown, it is a schematic diagram of the device structure in each step of the manufacturing method of the super junction device according to the embodiment of the present invention. Before forming the process, the following steps are included:

[0090] Step 1, such as Figure 4A As shown, the gate structure is formed, the gate structure is a trench gate, and the formation process of the trench gate includes:

[0091] A first epitaxial layer 2 with a first conductivity type is provided, and a photolithography process is performed to define a formation r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More