Method for affirming fatal fault in deep-sub-micrometer semiconductor device

A fatal defect, semiconductor technology, applied in the direction of single semiconductor device testing, semiconductor/solid-state device testing/measurement, test sample preparation, etc., can solve problems such as over-corrosion, difficult control, fast corrosion speed, etc., and achieve good repeatability , Ease of use

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0031] A method for confirming fatal defects in deep submicron semiconductor devices, comprising the following steps:

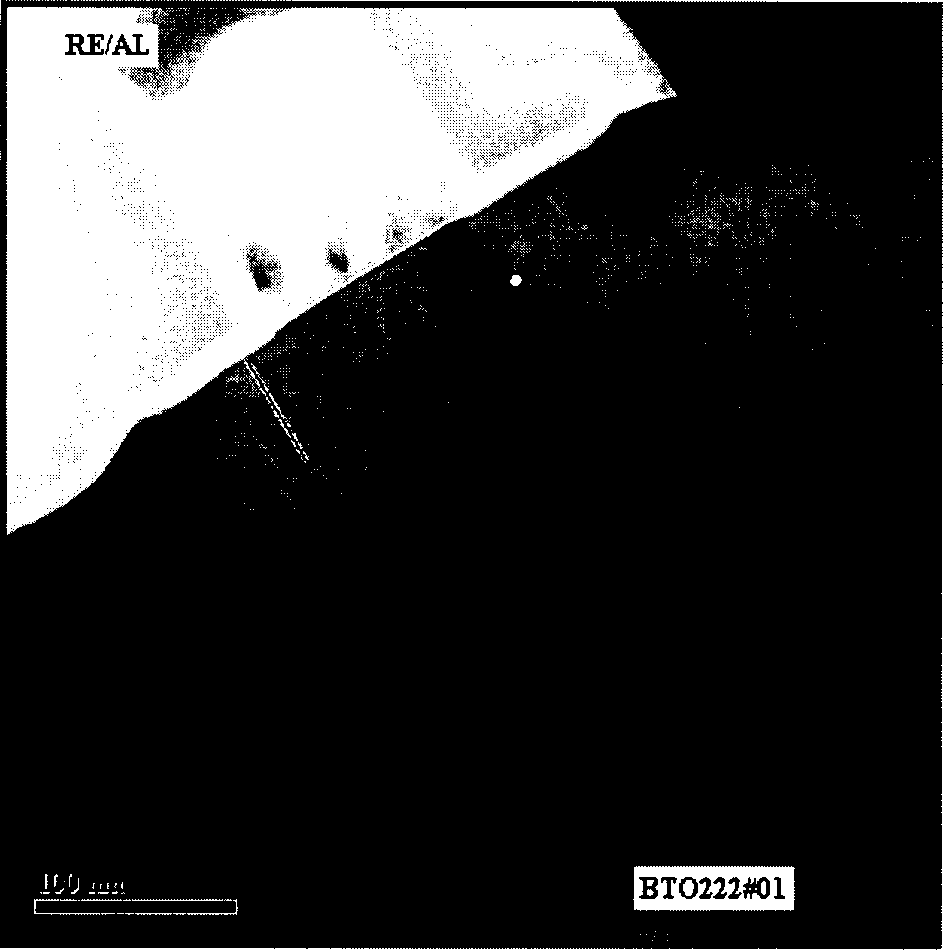

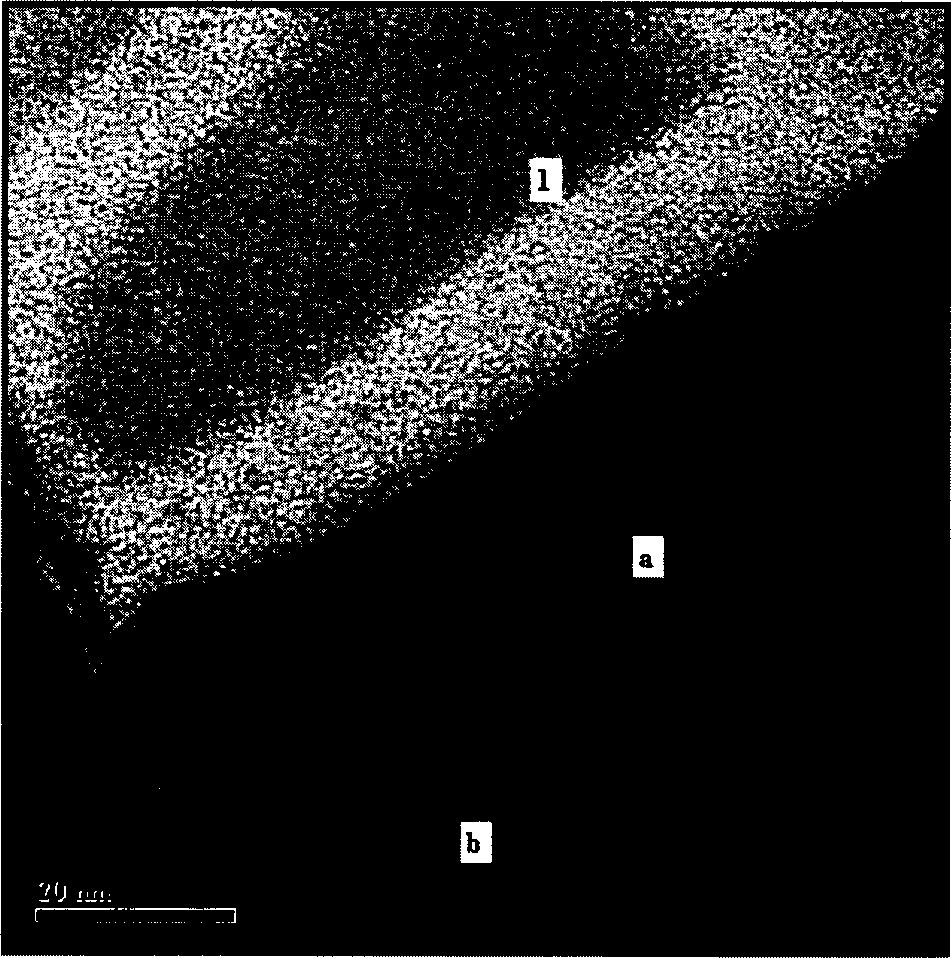

[0032] Step S101, prepare a transmission electron microscope (TEM) test sample with a focused ion beam (FIB) at the position confirmed by MOSAID / PVC, use a transmission electron microscope (TEM) to qualitatively locate and detect the semiconductor device sample, and determine whether there is Silicon crystal defect / dislocation defect, and determine the type of defect.

[0033] Step S102, if there is a defect in the semiconductor device, the sample is detected by the scanning electron microscope (SEM) of the present invention. The corrosion treatment solution corrodes the detection sample. Since the corrosion rates of each film layer in the semiconductor device are different, the corroded sample can be clearly Shows the structure of each film layer;

[0034] In step S103, the section of the sample is inspected by a scanning electron microscope (SEM), so as to...

Embodiment 2

[0037] Scanning electron microscope (SEM) detection sample corrosion treatment solution of another technical scheme of the present invention is, 65% nitric acid (HNO 3 )+acetic acid (CH 3 COOH)+49% hydrofluoric acid (HF)+copper nitrate (Cu(NO 3 ) 2 ) stirring and mixing the mixed acid solution formed.

[0038] The mixing ratio of each component in the mixed acid solution of the present invention is: 20ml 65% HNO 3 : 100mlCH 3 COOH: 1ml 49% HF: (0.8-1.2)gCu(NO 3 ) 2 .

[0039] In the mixed acid solution of the present invention, HNO 3 used as an oxidizing agent, CH 3 COOH was used as a buffer, HF was used as a complexing agent, Cu(NO 3 ) 2 Possesses electrochemical translocation function for improving HNO 3 +CH 3 A mixed acid solution of COOH+HF. The etching time of the mixed acid solution of the invention is appropriate, has an appropriate etching rate, and can ensure better repeatability.

Embodiment 3

[0041] The method for preparing sample by scanning electron microscope (SEM) detection sample corrosion treatment solution of the present invention may further comprise the steps:

[0042] Step 1, 20ml65% nitric acid (HNO 3 )+100ml acetic acid (CH 3 COOH)+1ml49% hydrofluoric acid (HF)+(0.8-1.2 grams) copper nitrate (Cu(NO 3 ) 2 ) stirring and mixing the mixed acid solution formed;

[0043] Step 2, cutting out the sample to be tested from the wafer, showing the profile of the specific position of the sample to be tested;

[0044] In step 3, the sample is soaked in the mixed acid solution prepared in step 1 for corrosion treatment. The time for soaking and corrosion treatment is about 5 seconds, and the corrosion time of the sample can be adjusted according to the sample preparation method used;

[0045] Step 4, the sample after corrosion treatment was rinsed with deionized water, and then dried.

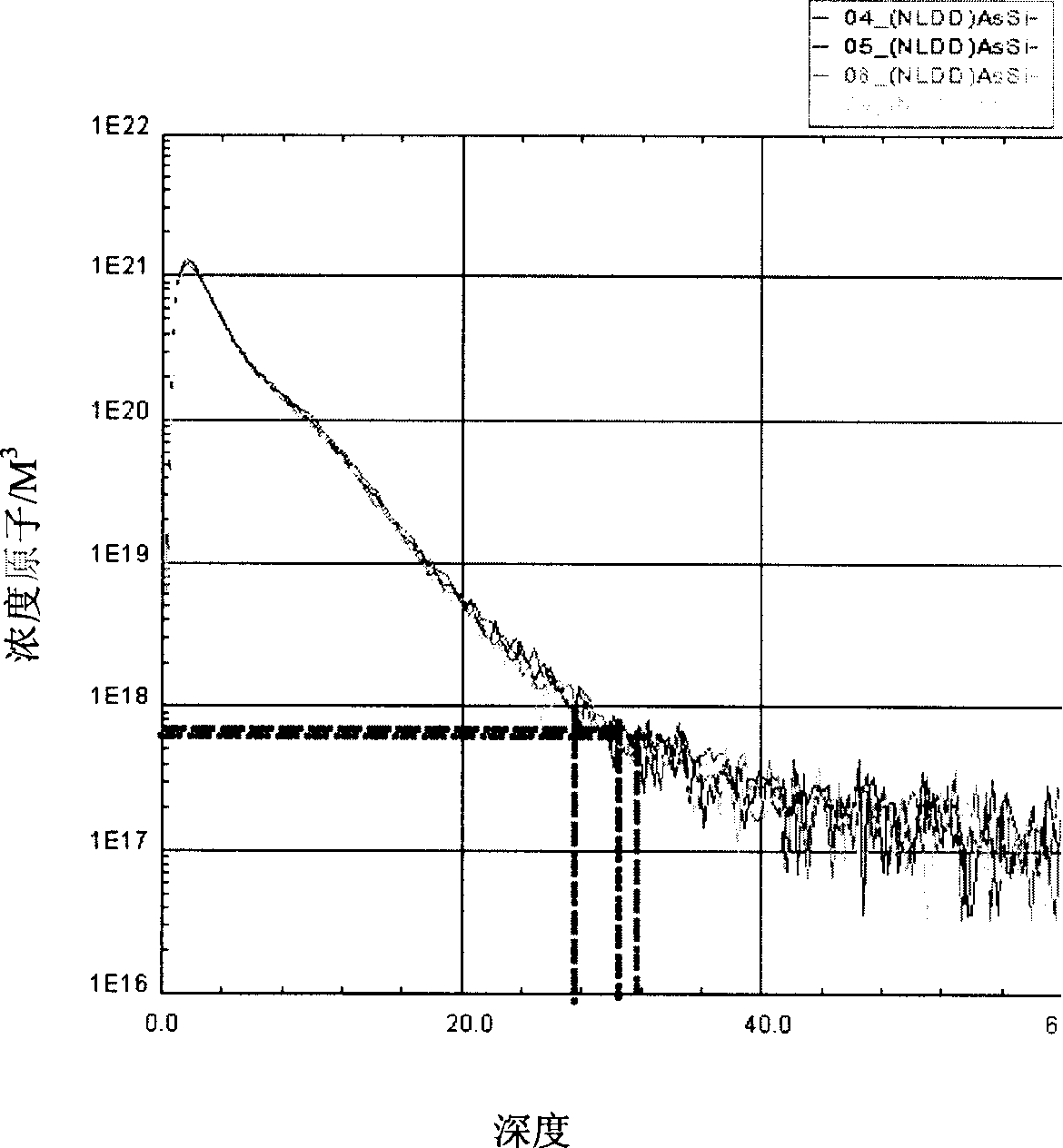

[0046] The contour of the lightly doped drain (NDD) region and the contour o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More