Stress silicon (Si) vertical-groove silicon-on-insulator bipolar complementary metal-oxide semiconductor (SOI BICMOS) integrated device and preparation method

A vertical channel, integrated device technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve the problems of low mechanical strength, high cost, incompatibility with wide application and development, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

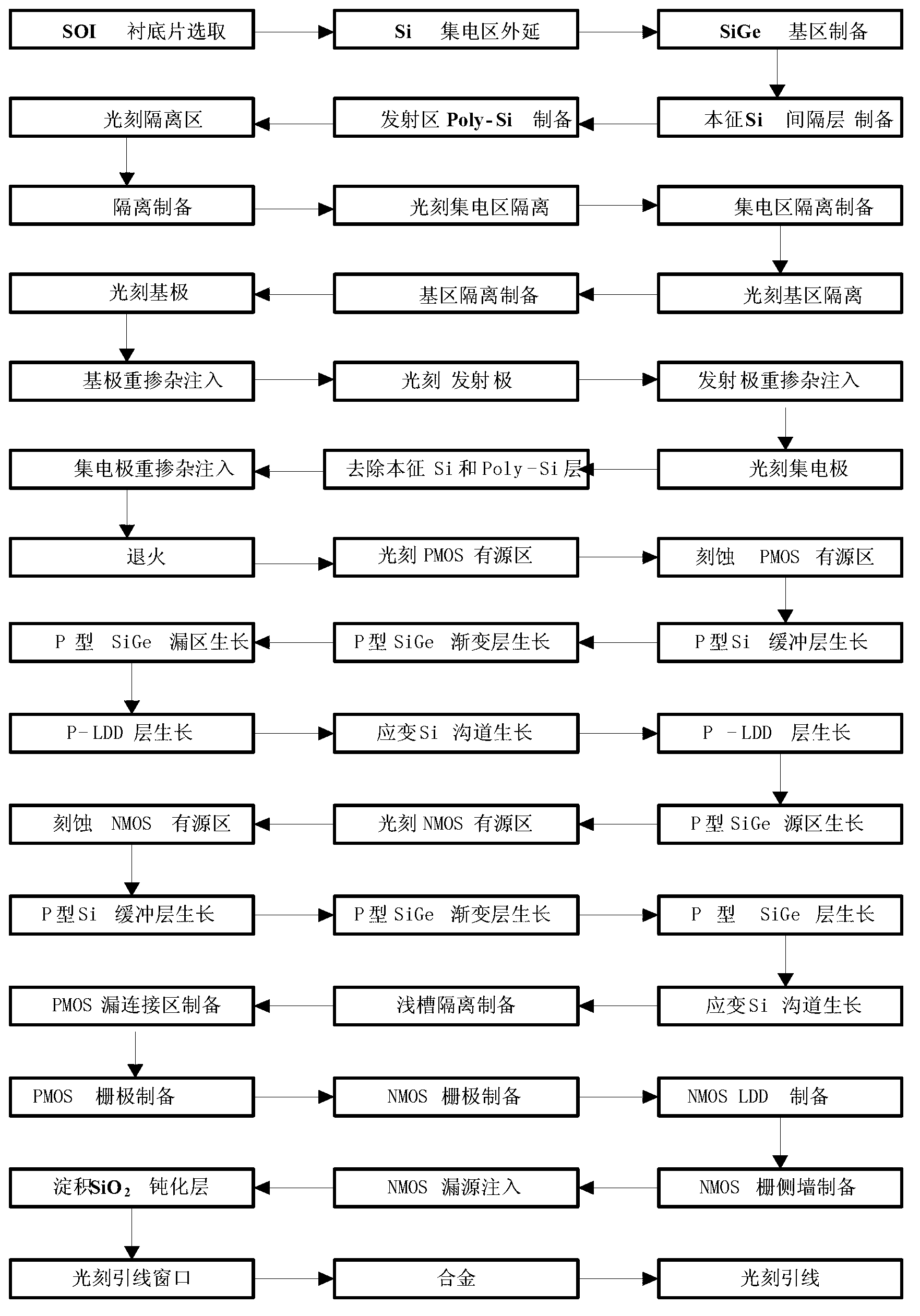

Image

Examples

Embodiment 1

[0124] Embodiment 1: The strained Si vertical channel SOI BiCMOS integrated device and circuit with a channel length of 22nm are prepared, and the specific steps are as follows:

[0125] Step 1, epitaxial material preparation.

[0126] (1a) Select the SOI substrate, the support material of the lower layer of the substrate is Si, and the middle layer is SiO 2 , with a thickness of 150nm, and the upper material is doped with a concentration of 1×10 16 cm -3 N-type Si with a thickness of 100nm;

[0127] (1b) Using the method of chemical vapor deposition (CVD), grow a layer of N-type epitaxial Si layer with a thickness of 250nm on the upper layer of Si material at 600°C, as the collector region, and the doping concentration of this layer is 1× 10 16 cm -3 ;

[0128] (1c) Using chemical vapor deposition (CVD), grow a SiGe layer with a thickness of 20nm on the substrate at 600°C. As the base region, the Ge composition of this layer is 15%, and the doping concentration is 5×10...

Embodiment 2

[0196] Embodiment 2: The strained Si vertical channel SOI BiCMOS integrated device and circuit with a channel length of 30nm are prepared, and the specific steps are as follows:

[0197] Step 1, epitaxial material preparation.

[0198] (1a) Select the SOI substrate, the support material of the lower layer of the substrate is Si, and the middle layer is SiO 2 , with a thickness of 300nm, and the upper material is doped with a concentration of 5×10 16 cm -3 N-type Si with a thickness of 120nm;

[0199] (1b) Using the chemical vapor deposition (CVD) method, at 700 ° C, grow a layer of N-type epitaxial Si layer with a thickness of 250 nm on the upper Si material, as the collector region, and the doping concentration of this layer is 5× 10 16 cm -3 ;

[0200] (1c) Using chemical vapor deposition (CVD), grow a layer of SiGe layer with a thickness of 40nm on the substrate at 700°C. As the base region, the Ge composition of this layer is 20%, and the doping concentration is 1×1...

Embodiment 3

[0268] Embodiment 3: The strained Si vertical channel SOI BiCMOS integrated device and circuit with the channel length of 45nm are prepared, and the specific steps are as follows:

[0269] Step 1, epitaxial material preparation.

[0270] (1a) Select the SOI substrate, the support material of the lower layer of the substrate is Si, and the middle layer is SiO 2 , with a thickness of 400nm, and the upper material is doped with a concentration of 1×10 17 cm -3 N-type Si with a thickness of 150nm;

[0271] (1b) Using chemical vapor deposition (CVD), grow a layer of N-type epitaxial Si layer with a thickness of 300nm on the upper layer of Si material at 750°C, as the collector region, and the doping concentration of this layer is 1× 10 17 cm -3 ;

[0272] (1c) Using chemical vapor deposition (CVD), grow a layer of SiGe layer with a thickness of 60nm on the substrate at 750°C. As the base region, the Ge composition of this layer is 25%, and the doping concentration is 5×10 1...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More