N-type MOS field-effect transistor and formation method thereof, semiconductor device and formation method of semiconductor device

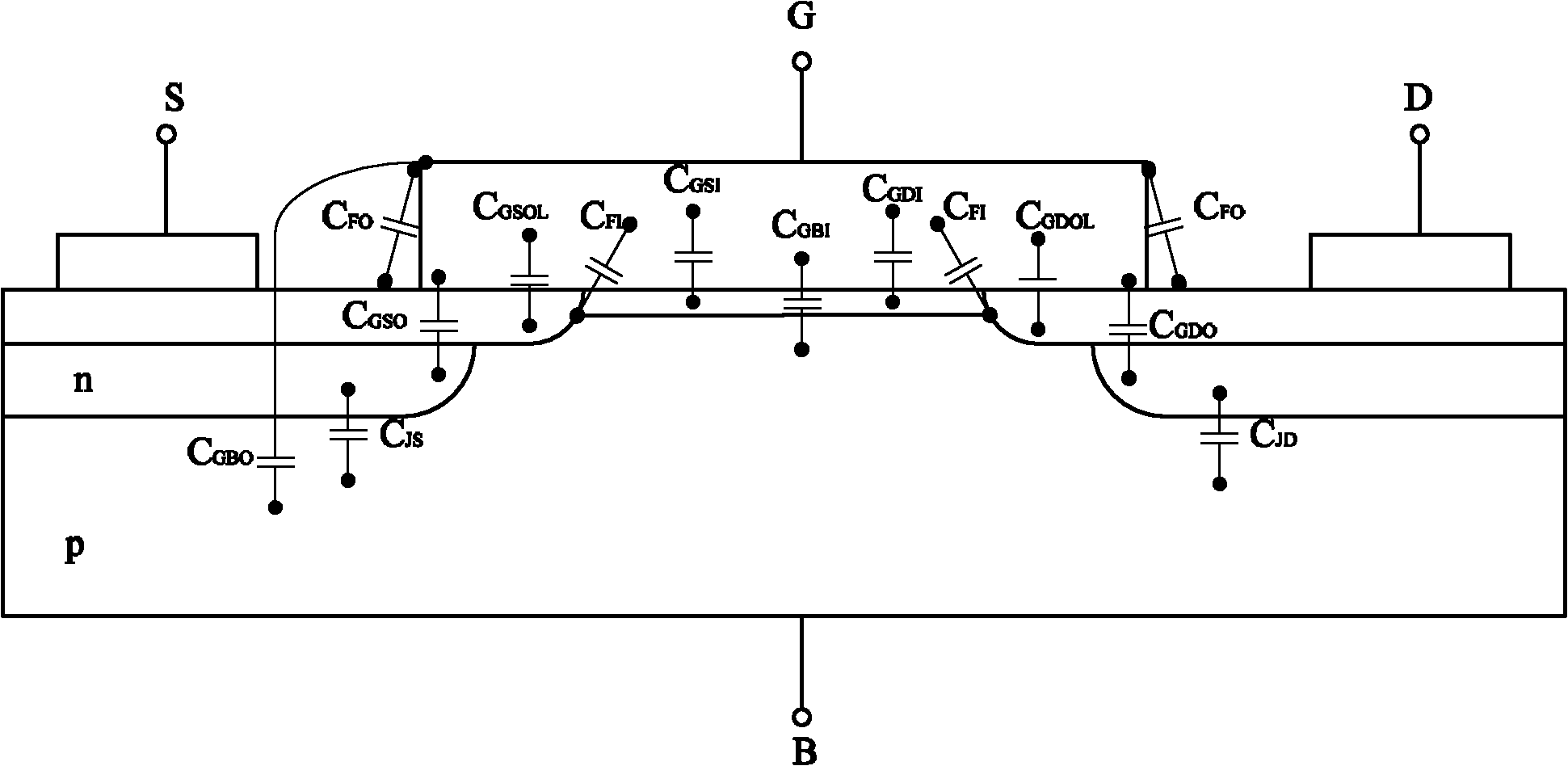

A field effect tube and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid state device manufacturing, electrical components, etc., can solve the problems of reducing the operating speed of integrated circuits, reducing the frequency of semiconductor device inverters, and n-type MOS field effect tubes Capacitance is too large to achieve the effect of increasing frequency, reducing overlapping capacitance, and reducing capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

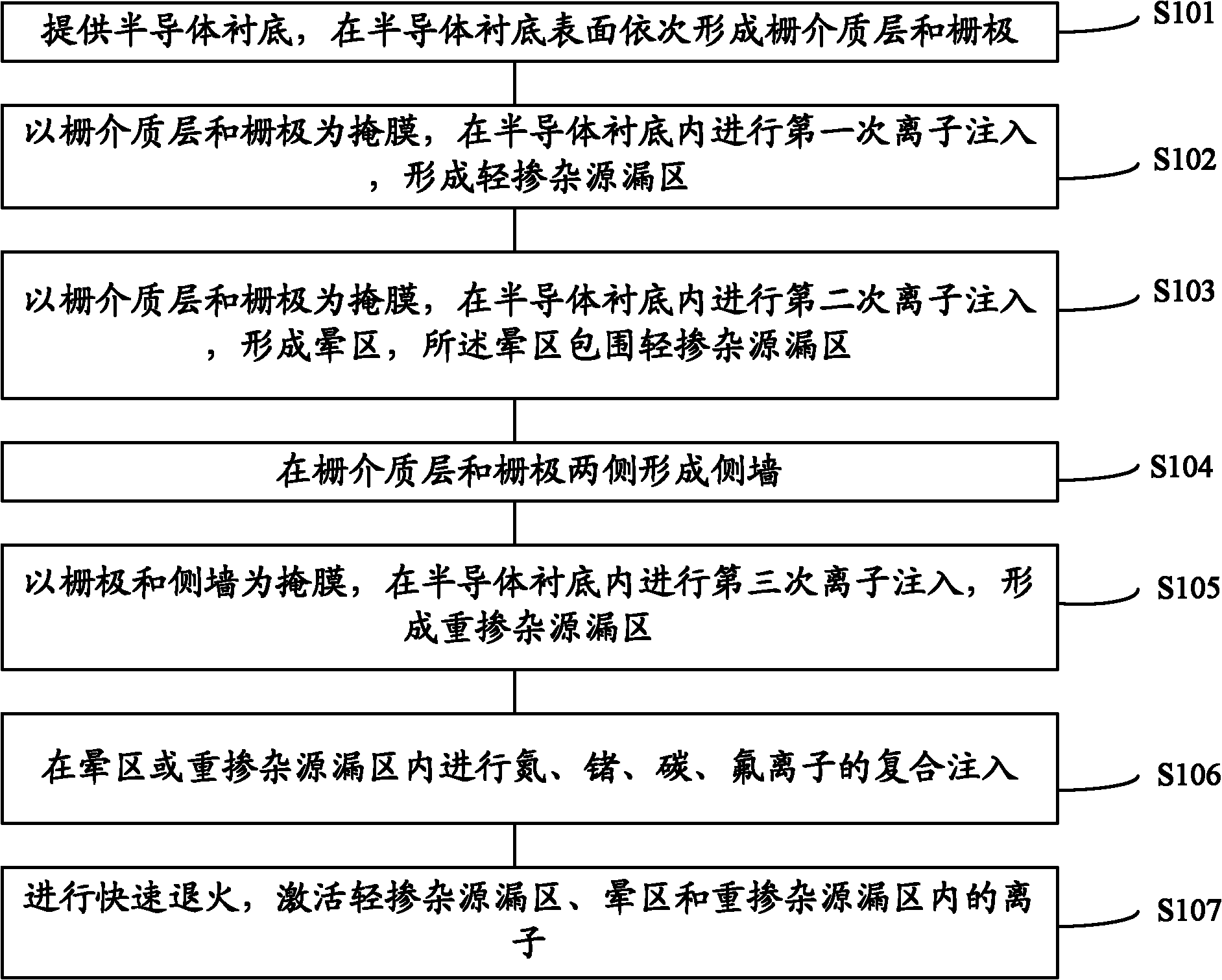

[0083] Figure 3 to Figure 8 It is a schematic cross-sectional structure diagram of the method for forming an n-type MOS field effect transistor according to Embodiment 1 of the present invention.

[0084] Please refer to image 3 A semiconductor substrate 100 is provided, and a gate dielectric layer 110 and a gate 111 are sequentially formed on the surface of the semiconductor substrate 100 .

[0085] The semiconductor substrate 100 may be made of silicon, germanium, gallium arsenide, silicon germanium or silicon-on-insulator, and p-type doping is performed in the semiconductor substrate 100 .

[0086] The formation process of the gate dielectric layer 110 and the gate 111 is as follows: a dielectric layer and a gate layer are sequentially formed on the surface of the semiconductor substrate 100, a photoresist is coated on the surface of the gate layer and patterned by exposure and development. To mask and etch the dielectric layer and the gate layer, remove the photoresist...

specific Embodiment 2

[0111] The method for forming the n-type MOS field effect transistor of the present invention will be described below in conjunction with the second embodiment.

[0112] Figure 9 , Figure 10 It is a schematic cross-sectional structure diagram of a method for forming an n-type MOS field effect transistor according to Embodiment 2 of the present invention.

[0113] Please refer to Figure 9 , providing a semiconductor substrate 300, sequentially forming a gate dielectric layer 310 and a gate 311 on the surface of the semiconductor substrate 300; using the gate dielectric layer 310 and the gate 311 as a mask, performing the first ion implantation in the semiconductor substrate 300 to form The lightly doped source and drain regions, and the second ion implantation form a halo region, and the halo region surrounds the lightly doped source and drain regions; perform rapid annealing to activate the ions in the lightly doped source and drain regions and the halo region, and the ac...

specific Embodiment 3

[0139] Figure 12 to Figure 18 It is a schematic cross-sectional structure diagram of a method for forming a semiconductor device according to Embodiment 3 of the present invention.

[0140] Please refer to Figure 12 , providing a semiconductor substrate 200, the semiconductor substrate has an n-type MOS field effect transistor region 201 and a p-type MOS field effect transistor region 202, and a gate dielectric layer 220 and a gate 221 are sequentially formed on the surface of the n-type MOS field effect transistor region 201 , forming a gate dielectric layer 222 and a gate 223 on the surface of the p-type MOS field effect transistor region 202 .

[0141] The n-type MOS field effect transistor region 201 and the p-type MOS field effect transistor region 202 are isolated by a shallow trench isolation structure 240 .

[0142] The semiconductor substrate 200 may be silicon, germanium, gallium arsenide, silicon germanium or silicon-on-insulator, p-type doping is performed on t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More