Controllable preparation method of germanium-silicon nano lower-dimension structure and germanium-silicon nano lower-dimension structure

A dimensional structure and nano technology, which is applied in the field of controllable preparation of germanium and silicon nanometer low-dimensional structure, can solve the difficulty of semiconductor device processing technology, cannot precisely control position, size, morphology, and composition, and cannot realize nanometer low-dimensional structure. The structure is completely controllable preparation and other problems, to achieve the effect of high repeatability, good controllability and simple process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

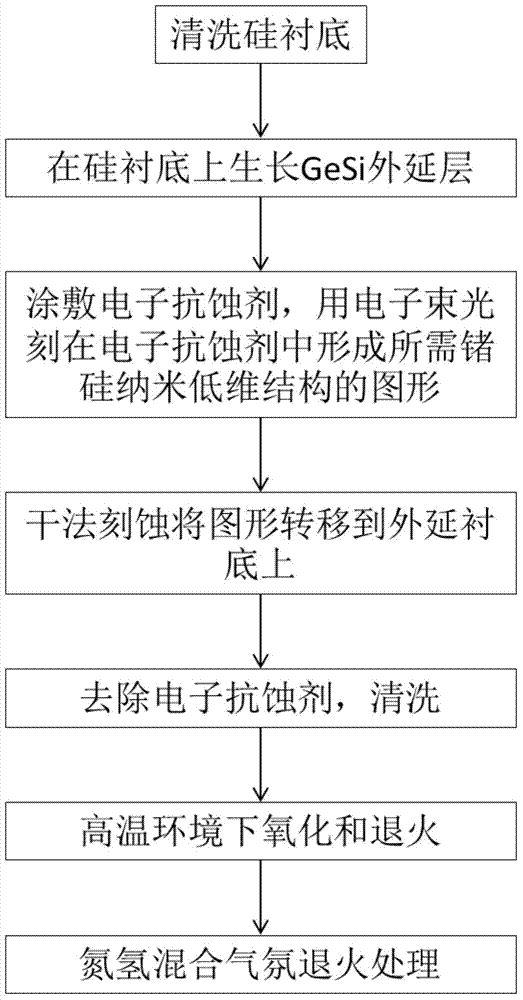

[0060] Periodically arranged silicon germanium nanowires with different sizes are prepared on the SOI substrate.

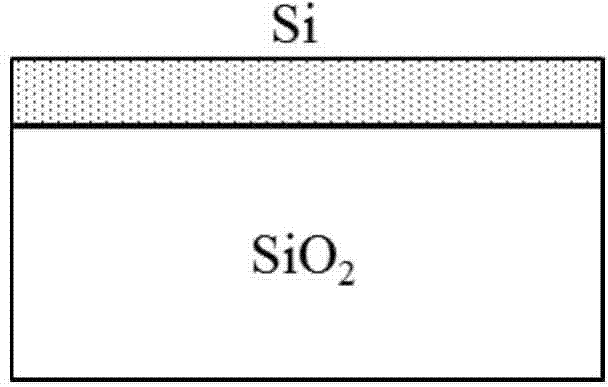

[0061] Such as diagram 2-1 As shown, the SOI substrate we selected (from bottom to top consists of a silicon base, a 3000nm thick buried oxide layer and a 55nm thick top layer silicon three-layer structure), and the substrate was cleaned by RCA process.

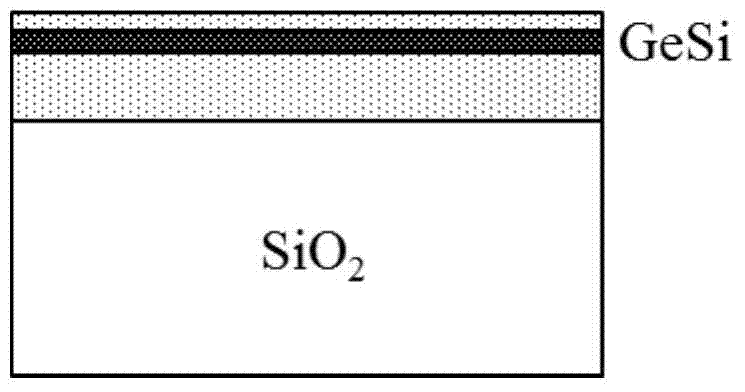

[0062] Figure 2-2 As shown, the SOI substrate is sent into the molecular beam epitaxy growth system, and 10nm silicon is grown at 450°C as a buffer layer, and then epitaxially grows Ge 0.1 Si 0.9 Quantum wells, 15nm thick, are finally covered with 5nm silicon. The molecular beam epitaxy system adopts the Eva-32 molecular beam epitaxy system of French Riber Company.

[0063] Figure 2-3 As shown, HSQ glue with a concentration of 3.6% is coated on the SOI substrate, the coating speed is 4000 rpm, and a hot plate is used for pre-baking at 150° C. for 4 minutes.

[0064] Figure 2-4 As shown, electron beam d...

Embodiment 2

[0070] Periodically arranged, germanium-silicon nanometer low-dimensional structures of different sizes are prepared on the SOI substrate.

[0071] Such as Pic 4-1 As shown, the SOI substrate we selected (from bottom to top is composed of a silicon base, a 3000nm thick buried oxide layer and a 53nm thick top layer silicon three-layer structure), and the substrate was cleaned by the RCA process.

[0072] Figure 4-2 As shown, the SOI substrate is sent into the molecular beam epitaxy growth system, and 10nm silicon is grown at 450°C as a buffer layer, and then epitaxially grows Ge 0.1 Si 0.9 Quantum wells, with a thickness of 30nm, are finally covered with 5nm silicon. The molecular beam epitaxy system adopts the Eva-32 molecular beam epitaxy system of French Riber Company.

[0073] Figure 4-3 As shown, the HSQ glue is coated on the SOI substrate, and pre-baked at 150°C for 4 minutes with a hot plate, and the thickness of the HSQ after baking is about 70nm.

[0074] Fi...

Embodiment 3

[0079] Periodically arranged, germanium-silicon nanometer low-dimensional structures of different sizes are prepared on the SOI substrate. According to the method provided by the invention, the concrete steps are:

[0080] Figure 6-1 As shown, the selected SOI substrate (from bottom to top consists of a silicon base, a 3000nm thick buried oxide layer and a 50nm thick top silicon three-layer structure), and the substrate is cleaned by RCA process.

[0081] Figure 6-2 As shown, the SOI substrate was sent into the ultra-high vacuum vapor deposition system, and 10nm silicon was grown as a buffer layer, and then epitaxially grown Ge 0.2 Si 0.8 Quantum wells, with a thickness of 30nm, are finally covered with 10nm silicon. Figure 6-3 As shown, ZEP520 glue is coated on the SOI substrate, the coating speed is 2000rpm, and a hot plate is used for pre-baking at 180°C for 3 minutes. After baking, the thickness of ZEP520 is about 90nm.

[0082] Figure 6-4 As shown, electron beam...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com