Electrically erasable programmable read-only memory (EEPROM)

A storage unit and capacitor technology, applied in electrical components, electric solid devices, circuits, etc., can solve problems such as unfavorable chip working field strength, information loss, wrong writing, etc., to improve data storage capabilities, improve data storage capabilities, The effect of operating voltage reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

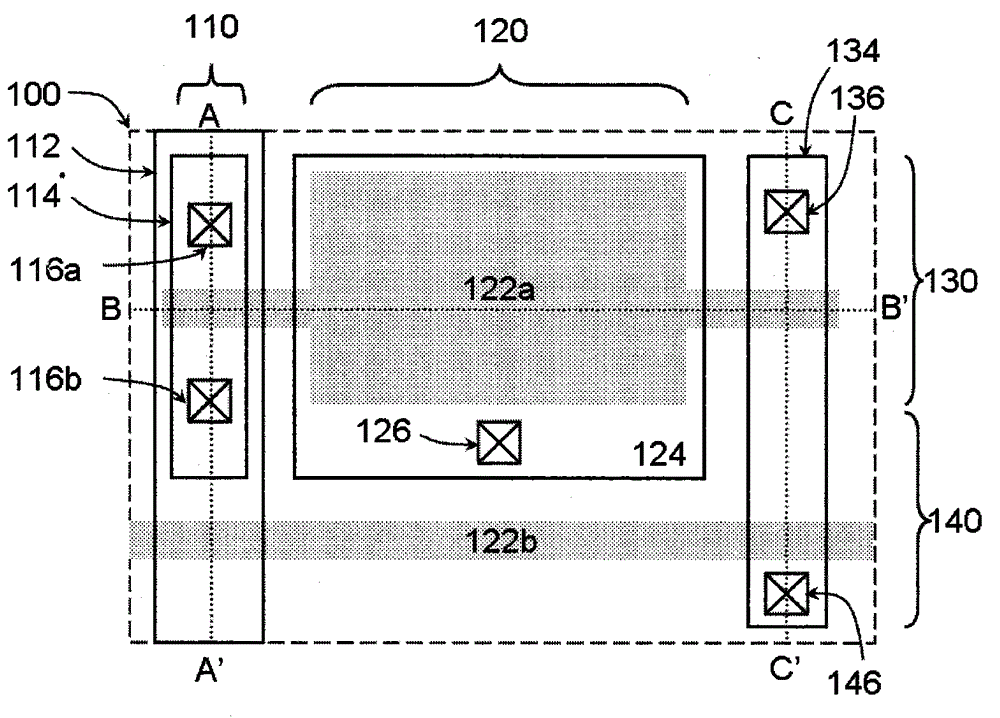

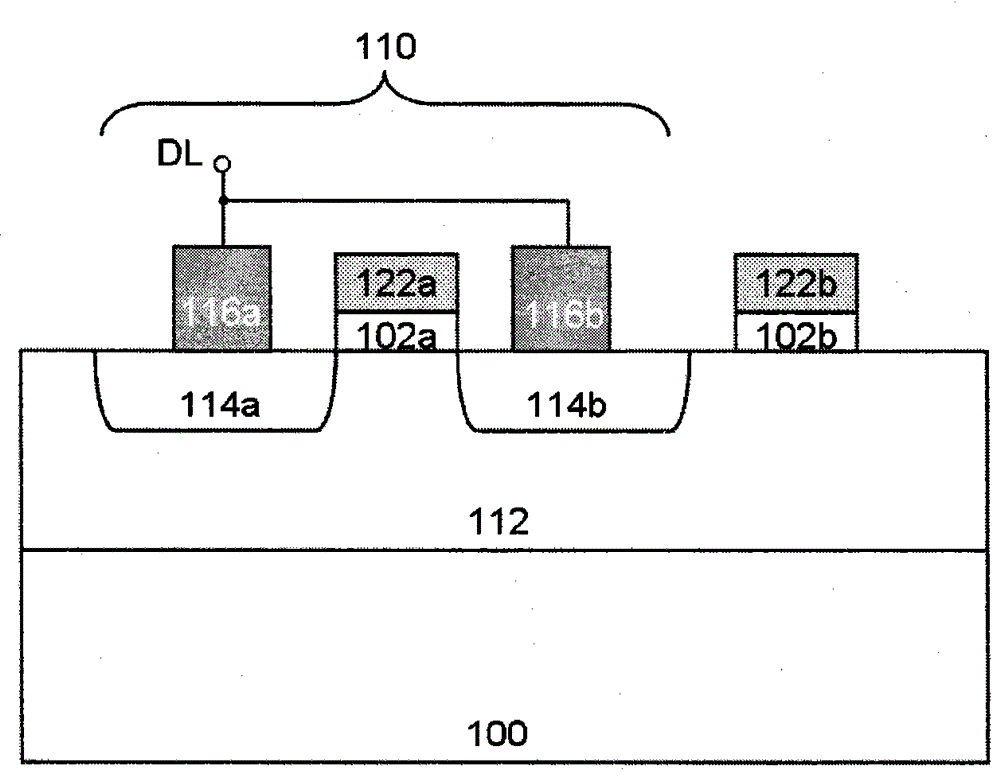

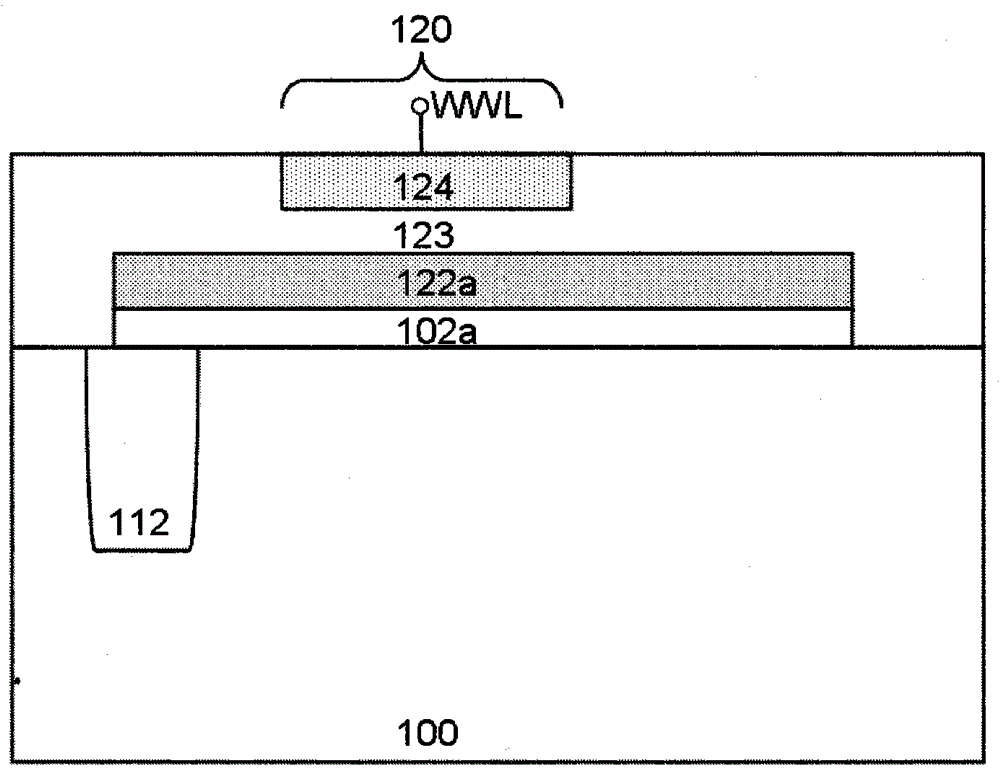

[0020] Such as figure 1 A kind of EEPROM storage unit shown, described semiconductor substrate is the epitaxial silicon slice 100 of P-type doping, the PMOS electric capacity 110, polysilicon electric capacity 120, NMOS selector tube 130, NMOS reading tube 140 formed on the semiconductor substrate; The PMOS capacitor 110 includes: an n-well 112 formed by ion implantation on a p-type doped epitaxial silicon wafer 100, a first gate oxide layer 102a, a second gate oxide layer 102b, a floating gate 122a placed on the first gate oxide layer 102a, a source drain Region one 114a, source drain region two 114b, MOS capacitor contact hole one 116a placed on source drain region one 114a and MOS capacitor contact hole two 116b placed on source drain region two 114b, the floating gate 122a is used as a PMOS capacitor The first MOS capacitor contact hole 116a and the second MOS capacitor contact hole 116b are short-circuited for connecting DL, and the first source-drain region 114a and the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com