Method for treating ILD (injection laser diode) layer in gate-last technology

A processing method and gate-last process technology, applied to semiconductor devices, electrical components, circuits, etc., can solve problems such as small process windows, affecting device performance, and difficulty in control, so as to reduce the difficulty of device integration, improve the process window, and improve the cost efficiency. effect of density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

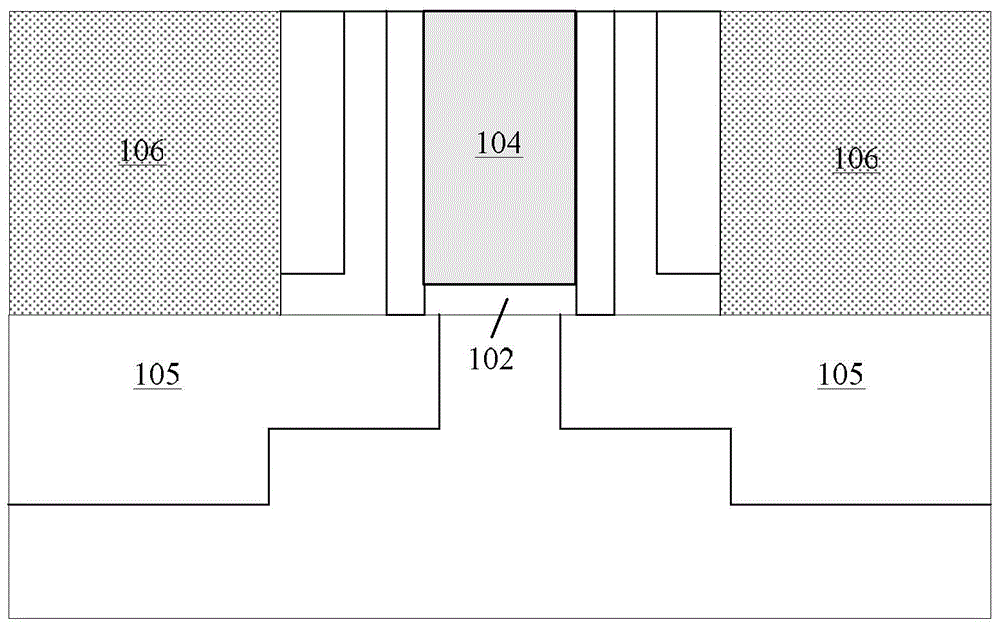

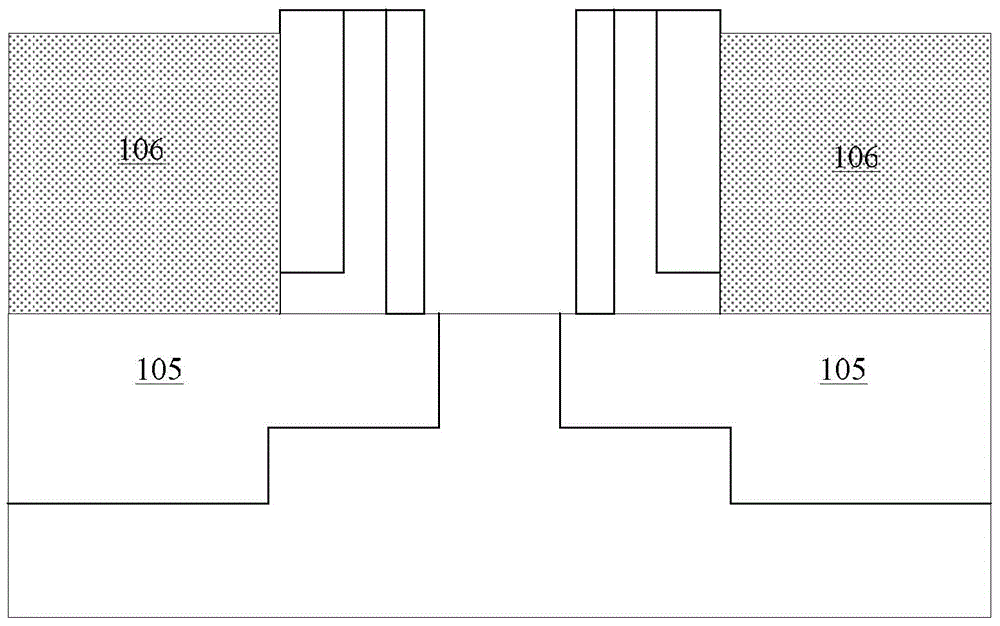

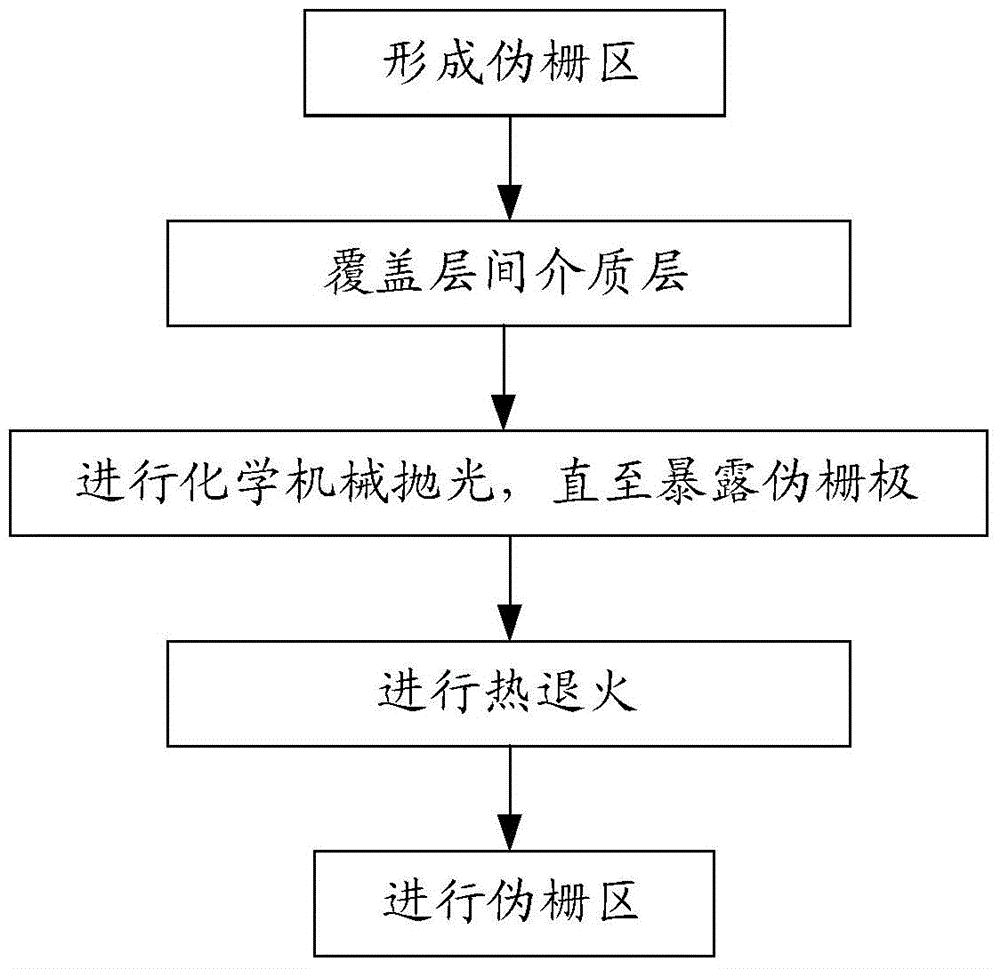

[0028] The invention mainly aims at the loss of the ILD layer in the process of removing the dummy gate dielectric layer in the gate-last process. Generally, in the gate-last process, before forming the ILD layer, it mainly includes the following step S101 of forming a dummy gate device:

[0029] provide the substrate;

[0030] sequentially forming a dummy gate dielectric layer and a dummy gate on the substrate;

[0031] A spacer is formed on the sidewall of the dummy gate, and a source drain is formed on both sides of the dummy gate.

[0032] In the embodiment of the present invention, refer to Figure 4 As shown, the semiconductor substrate 200 may be a Si substrate, a Ge substrate, a Si-Ge substrate, SOI (Silicon On Insulator, Silicon On Insulator) or GOI (Germanium On Insulator, Germanium On Insulator) and the like. In other embodiments, the semiconductor substrate may also be a substrate including other elemental semiconductors or compound semiconductors, such as GaAs,...

Embodiment 2

[0047] The formation method of the first embodiment of the present invention has been described in detail above. In the second embodiment, the difference from the first embodiment is that after the CMP of the ILD, the nitriding treatment is performed first, and then the thermal annealing is performed, thereby improving the ILD. corrosion resistance. Only the differences will be described below, and other similarities with Embodiment 1 will not be repeated.

[0048] In step S201, a dummy gate device is formed, which is the same as step S101 in the first embodiment.

[0049] Then, in step S202 , the source and drain regions are covered, and further chemical polishing is performed to form an ILD (Inter Layer Dielectric) layer, which is the same as step S102 in the first embodiment.

[0050] Then, in step S2021, nitriding treatment is performed.

[0051] In this embodiment, DPN (decoupled plasma nitriding, decoupled plasma nitriding) is used for nitriding treatment, so that the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com