Preparation method for field effect transistor

A field-effect transistor and semiconductor technology, applied in the field of electronics, can solve the problems of difficulty in realizing flexibility, large-area devices, unstable electrical performance, and complicated preparation process, and achieves a technology that prevents ultraviolet and electromagnetic radiation, is easy to implement, and has a simple preparation process. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

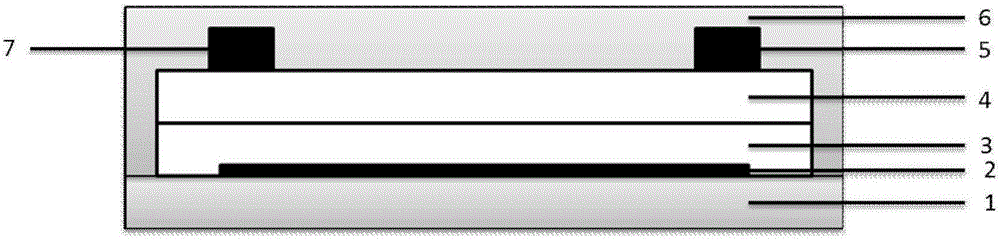

[0047] like figure 1 The bottom gate top contact structure is shown, the material and thickness of each layer are: the substrate is shellac, the gate electrode, source electrode and drain electrode are all silver nanowires, adding 10% shellac and 30% water soluble The adhesive is gelatin, the dielectric layer adopts mica sheet, the thickness is 5nm, the semiconductor layer is zinc oxide, the thickness is 30nm, and the encapsulation layer is shellac. With this structure, a field effect transistor with high lifetime and high stability can be realized.

[0048] The preparation method is as follows:

[0049] ①Clean the mica sheet thoroughly first, then dry it after cleaning;

[0050] ②Preparing the silver nano wire grid electrode 2 on the mica surface by screen printing technology, and curing it;

[0051] ③ Prepare a shellac layer on the grid electrode 2, and rapidly increase the heating temperature of the device to 70°C to 90°C, so that the shellac layer is in a hot-melt state, ...

Embodiment 2

[0058] like figure 1 The bottom gate top contact structure is shown, the material and thickness of each layer are: the substrate is shellac, the gate electrode, source electrode and drain electrode are all aluminum nanowires, and 30% shellac and 30% water soluble The non-toxic adhesive polyvinyl alcohol, the dielectric layer adopts silk fibroin sheet, the thickness is 8nm, the semiconductor layer is graphene oxide, the thickness is 30nm, and the encapsulation layer is shellac. With this structure, a field effect transistor with high lifetime and high stability can be realized.

[0059] Preparation method is like embodiment 1.

Embodiment 3

[0061] like figure 1 Shown is the bottom gate top contact structure, the material and thickness of each layer are: the substrate is shellac, the gate electrode, source electrode and drain electrode are all gold nanowires, adding 30% shellac and 10% water soluble The adhesive is gelatin, the dielectric layer adopts hexagonal boron nitride, the thickness is 10nm, the semiconductor layer is carbon nanotube, the thickness is 50nm, and the encapsulation layer is shellac. With this structure, a field effect transistor with high lifetime and high stability can be realized.

[0062] Preparation method is like embodiment 1.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More