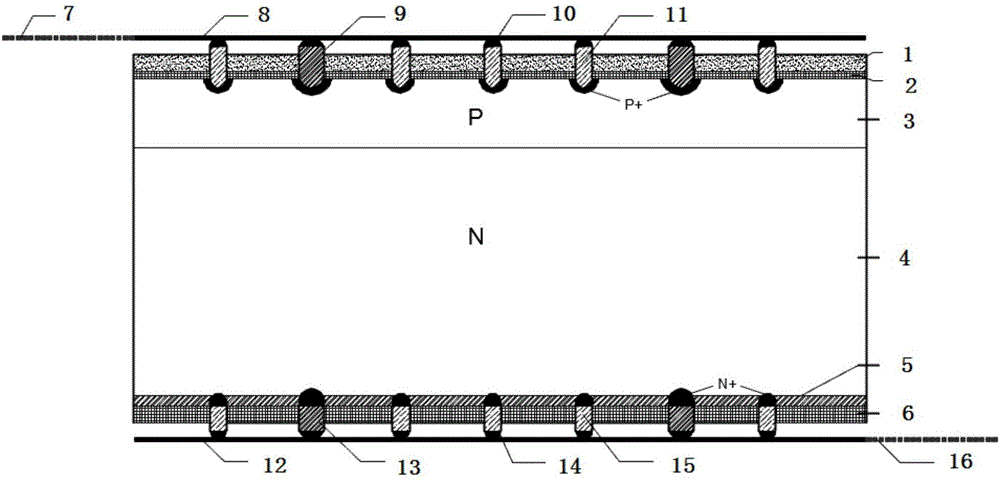

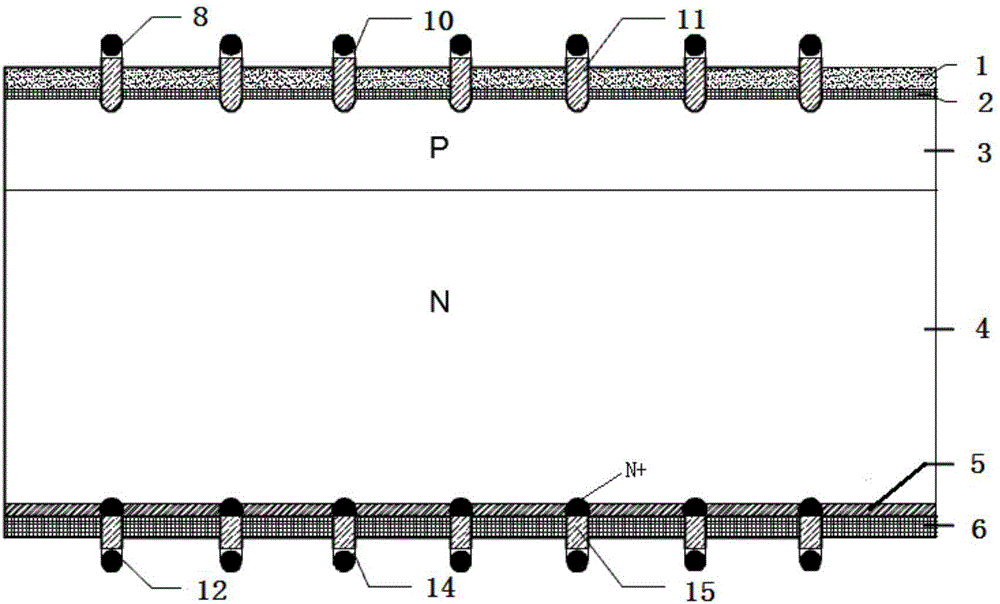

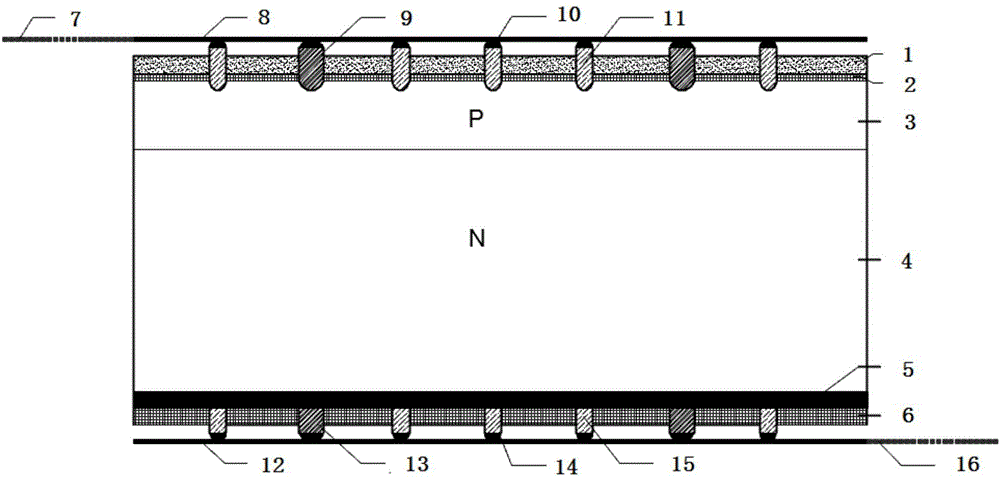

N-type crystalline silicon double-sided solar cell structure and preparation method thereof

A technology for solar cells and crystalline silicon, applied in the field of solar cells, can solve the problems of no application, increased process complexity, unsuitable for industrialized production of N-type crystalline silicon cells, etc. small effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0067] (1) The N-type monocrystalline silicon wafer is anisotropically etched in a KOH solution at about 80°C to obtain a pyramid structure on the surface.

[0068] (2) On the front side of the silicon wafer, with BBr 3 As an impurity, it is diffused at a low pressure at about 950°C to form a uniform diffusion layer of 40Ω / □.

[0069] (3) On the back of the silicon wafer, POCl 3 As an impurity, it is diffused under low pressure at about 800°C to form a uniform diffusion layer of 40Ω / □.

[0070] (4) Spray a mask on the front and back of the silicon wafer according to a specific pattern. The pattern of the front and back masks is a combination of four equidistant main grids and arrayed line segments, where the width of a single line segment is 40um, the length is 0.5mm, and the distance between two adjacent line segments in the same row is 0.5mm. The distance between two adjacent line segments in the same column is 1.5mm. The busbar has a width of 1.2mm and a length of 156mm...

Embodiment 2

[0082] (1) N-type monocrystalline silicon wafers are anisotropically etched in a KOH solution at about 80°C to obtain a pyramid structure on the surface.

[0083] (2) Coating boron paste on the front side of the silicon wafer.

[0084] (3) Dry the boron paste on the front side of the silicon wafer.

[0085] (4) Print phosphor paste on the back of the silicon wafer according to a specific pattern. The printed pattern is a line segment distributed in an array. The width of a single line segment is 50um and the length is 3mm. The distance between two adjacent line segments in the same row is 2mm. The distance between two adjacent line segments is 3mm.

[0086] (5) Dry the phosphorous slurry in the local area on the back of the silicon wafer.

[0087] (6) Heat treatment at about 950°C to diffuse boron atoms on the front of the silicon wafer and phosphorus atoms on the back to the silicon substrate, thereby forming a uniform P-type diffusion layer of 100Ω / □ on the front of the si...

Embodiment 3

[0099] (1) N-type monocrystalline silicon wafers are anisotropically etched in NaOH solution at about 80°C to obtain a surface pyramid structure.

[0100] (2) Boron atoms are doped on the front side of the N-type silicon wafer by ion implantation, and the boron source is BF 3 , forming a uniform diffusion layer of 80Ω / □.

[0101] (3) Phosphorus atoms are doped on the back of the N-type silicon wafer by ion implantation, and the boron source is PH 3 , forming a uniform diffusion layer of 70Ω / □.

[0102] (4) Chemically cleaning the silicon wafer after ion implantation.

[0103] (5) Aluminum oxide of about 3nm is deposited on the front, and then silicon nitride of about 80nm is deposited; silicon nitride of about 80nm is deposited on the back.

[0104] (6) On the front side of the silicon wafer, use screen printing method to prepare partial contact metal electrodes on the front side according to the array distribution pattern. The printed pattern is a dot array, the diameter o...

PUM

| Property | Measurement | Unit |

|---|---|---|

| length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More