Annealing method for heterojunction solar cell

A solar cell and heterojunction technology, which is applied in circuits, photovoltaic power generation, electrical components, etc., can solve the problems of difficult process, small annealing process interval of heterojunction solar cells, high requirements for sintering process and silver paste, and achieve technological The process is simple, the contact resistance and surface work function are reduced, and the effect of improving battery performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

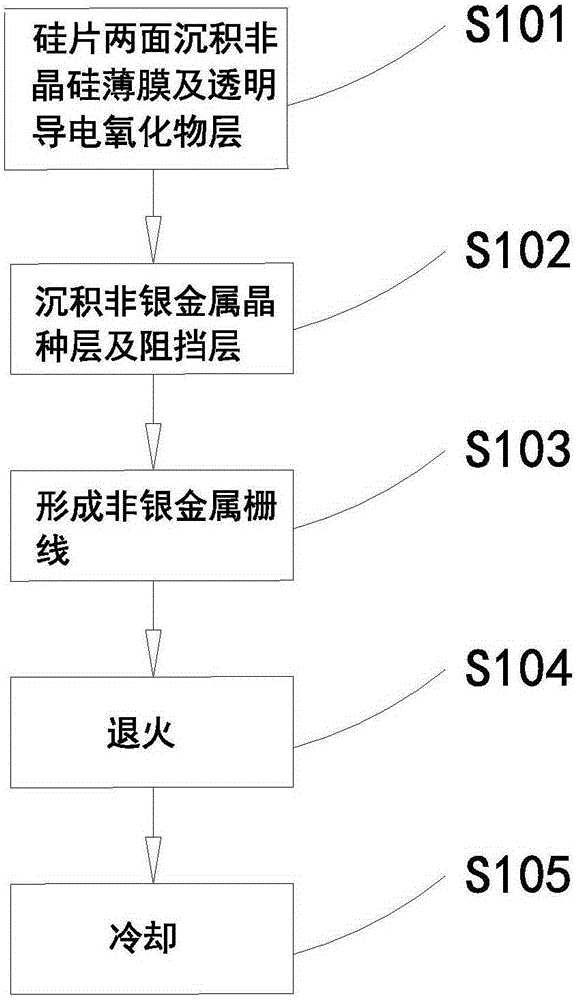

[0035] Such as figure 1 Shown:

[0036] Step S101, depositing a thin intrinsic amorphous silicon layer and an n-type amorphous silicon layer of 10 nm in total on one side of the textured and cleaned n-type silicon substrate, and depositing a thin intrinsic amorphous silicon layer and p A total of 10 nm of non-crystalline silicon layer, and then deposit a transparent conductive oxide ITO thin film of 100 nm on the thin amorphous silicon layer on both sides of the silicon wafer.

[0037] Step S102 , depositing a barrier layer and a 100 nm seed layer by magnetron sputtering on the transparent conductive oxide ITO layer in step S101 .

[0038] Step S103 , forming Cu gate lines on the barrier layer and the seed layer deposited by magnetron sputtering in step S102 by patterning and electrochemical deposition processes.

[0039] Step S104, place the solar cell with the Cu grid lines formed in step S103 in a temperature range of 170°C to 190°C for annealing, the annealing atmosphere...

Embodiment 2

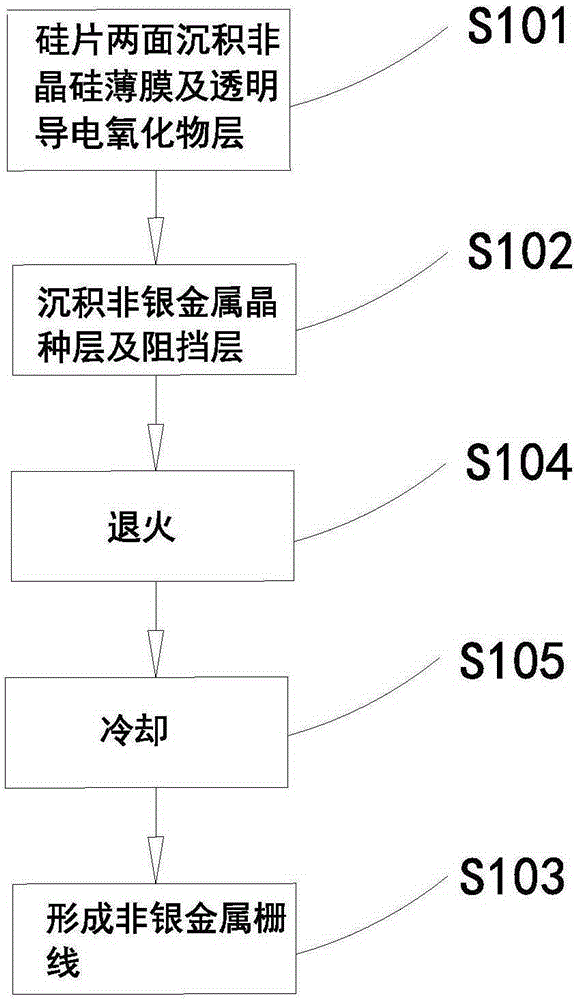

[0042] Such as figure 2 Shown:

[0043] Step S101, depositing a thin intrinsic amorphous silicon layer and a p-type amorphous silicon layer with a total thickness of 10 nm on one side of the p-type silicon substrate having a suede surface after cleaning, and depositing a thin intrinsic amorphous silicon layer and n Type amorphous silicon layer with a total of 10nm, and then deposit a transparent conductive oxide ITO thin film of 90nm on the amorphous silicon thin layer on both sides.

[0044]Step S102 , depositing a barrier layer and a seed layer of 150 nm by magnetron sputtering on the transparent conductive oxide ITO layer.

[0045] Step S104, place the battery semi-finished sheet deposited with the barrier layer and the seed layer at a temperature range of 170°C to 190°C for annealing, the annealing atmosphere is nitrogen, the annealing time is 50 minutes, the annealing pressure is 300 torr, and the whole annealing process is under oxygen The content in the annealing atm...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More