GaN-based heterojunction integrated device structure and manufacturing method

A GaN-based, device structure technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as low efficiency, small contact area between gate and AlGaN, device burnout failure, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

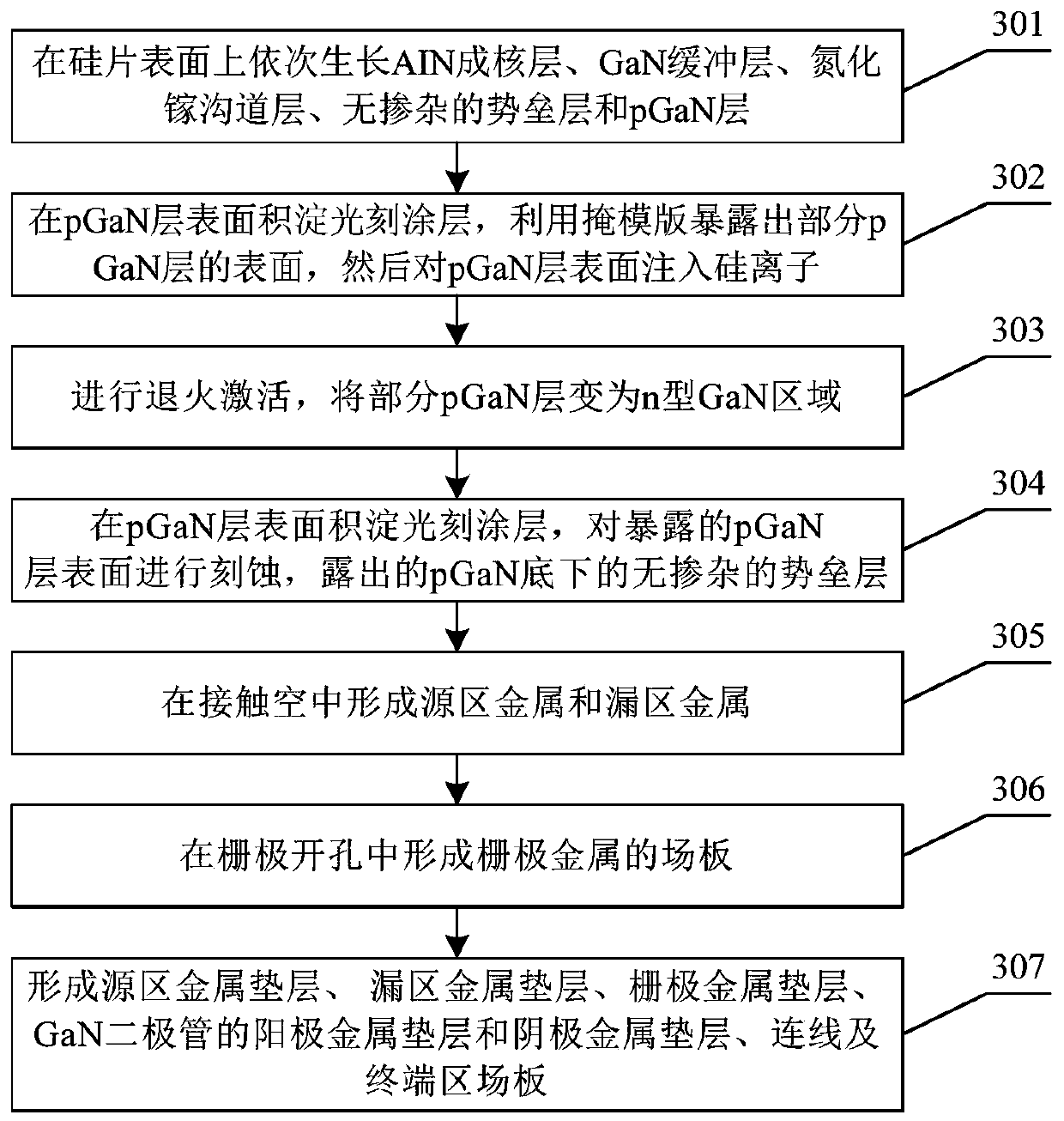

[0062] image 3 It is a flow chart of the manufacturing method of the gallium nitride-based heterojunction integrated device structure of the present invention, which will be referred to below image 3 , the method for manufacturing the GaN-based heterojunction integrated device structure of the present invention is described in detail.

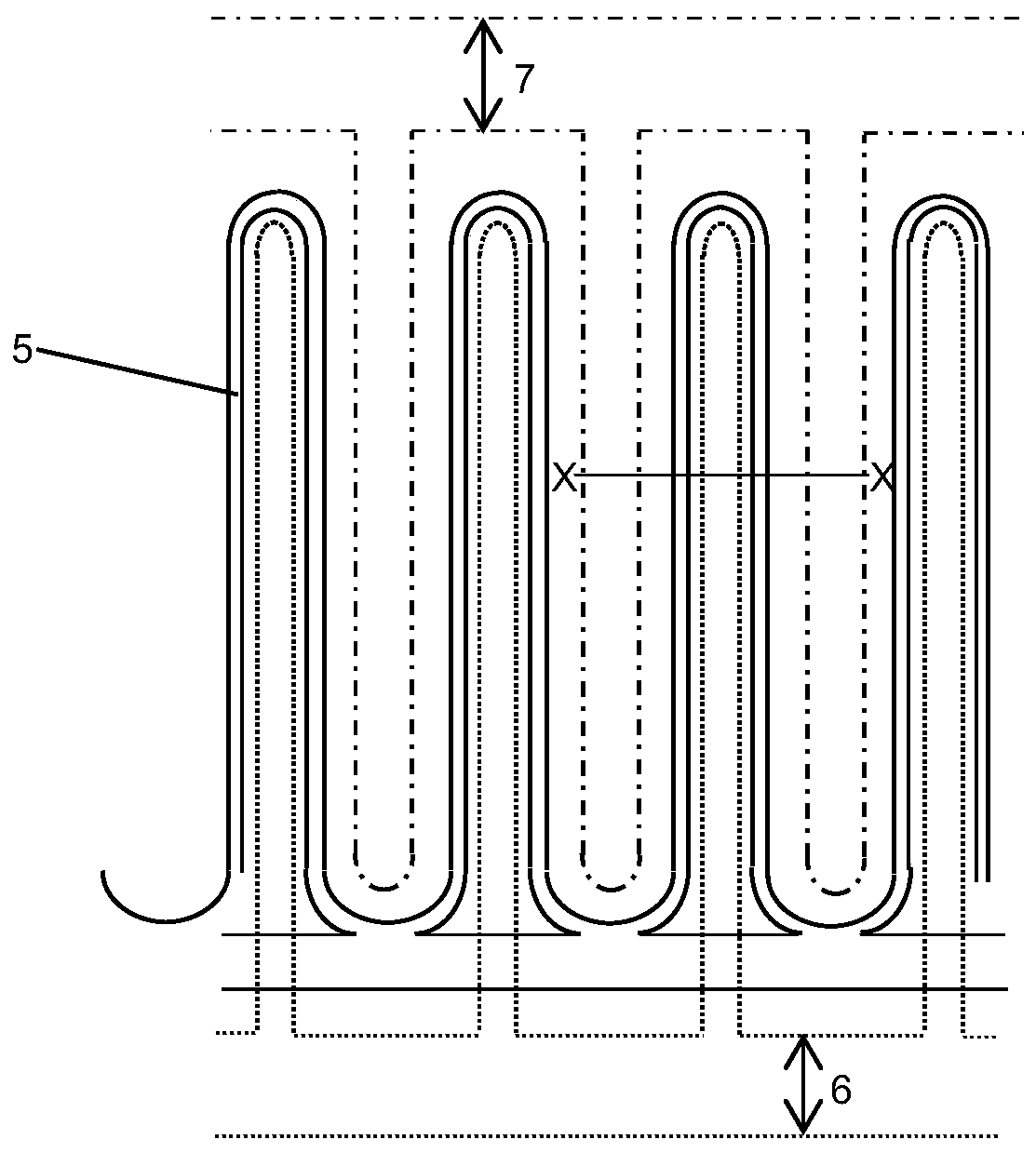

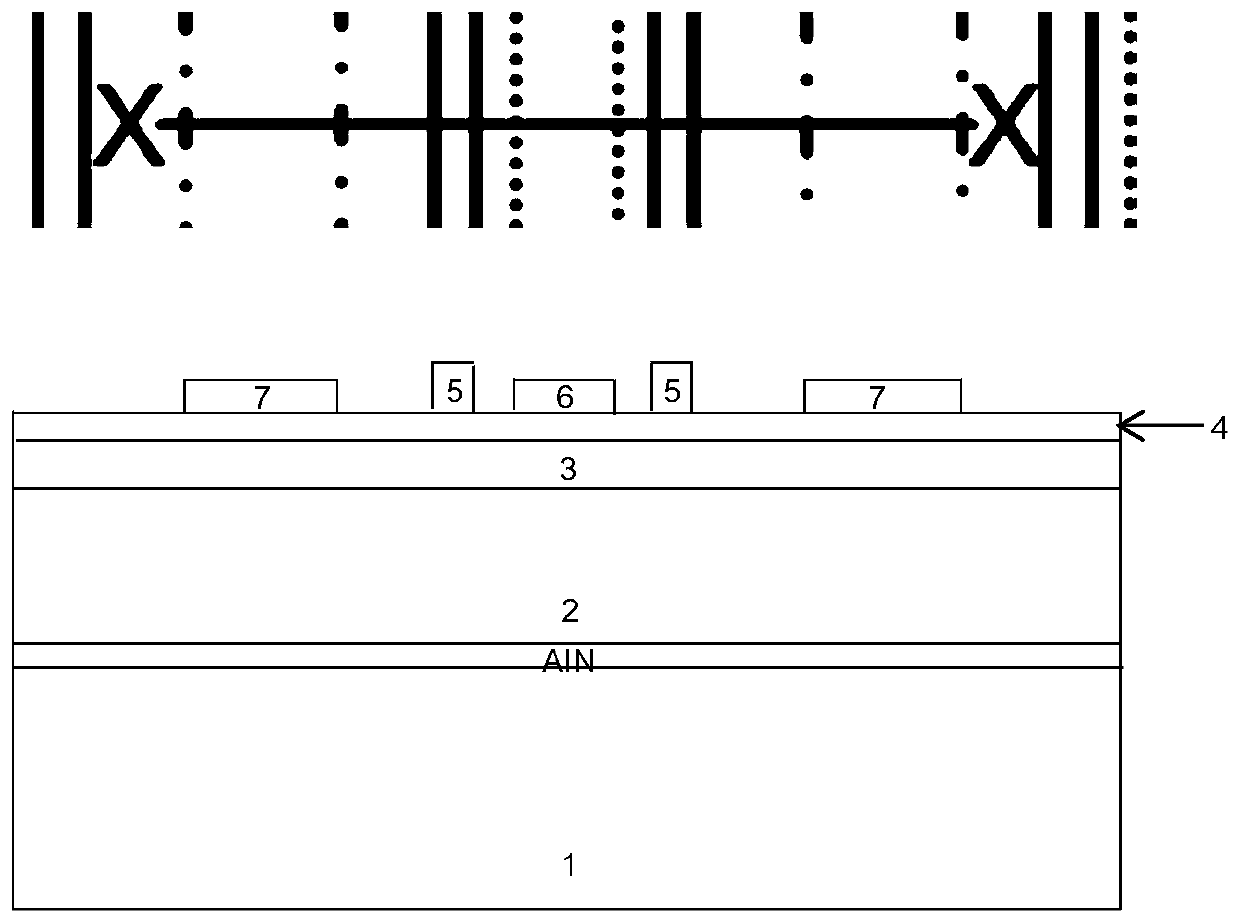

[0063] First, in step 301, an AlN nucleation layer, a GaN buffer layer 2, a gallium nitride channel layer (GaN Channel) 3, an undoped barrier layer 4 and a pGaN layer 5 are sequentially grown on the surface of the silicon wafer.

[0064] Figure 4 It is a schematic cross-sectional view of an embodiment of the present invention after all epitaxial layers are completed, such as Figure 4 As shown, in the embodiment of the present invention, a 200nm AlN nucleation layer, a 4um unintentionally doped GaN buffer layer 2, and a 300nm gallium nitride channel layer (GaNChannel) are sequentially grown on the surface of the silicon wafer 1 by the MOCV...

Embodiment 2

[0081] Figure 17 For the present invention connects the cross-section schematic diagram of each electrode in the integrated device structure with metal wire, as Figure 17 As shown, wherein, G is the gate of the transistor, S is the source of the transistor, D is the drain of the transistor, A is the anode of the gallium nitride-based pn junction diode, and C is the cathode of the gallium nitride-based pn junction diode.

[0082] The gallium nitride-based heterojunction field effect transistor structure of the present invention is to integrate a gallium nitride-based pn junction diode (GaN diode) on the original device, and the HEMT transistor in the integrated device can be integrated with the gallium nitride-based pn junction diode. The junction diodes are connected together with metal wires, for example, the drain D of the HEMT transistor is connected to the anode A of the GaN-based pn junction diode, and the source S of the HEMT transistor is connected to the cathode C of...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com