Preparation method of silicon carbide N-channel bipolar power device

A power device, bipolar technology, applied in the field of silicon carbide N-channel bipolar power device preparation, can solve the problems of increasing device on-resistance, rough back surface, thick wafer epitaxial wafer, etc., and achieve good ohm Effects of contact, cost savings, and ease of preparation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

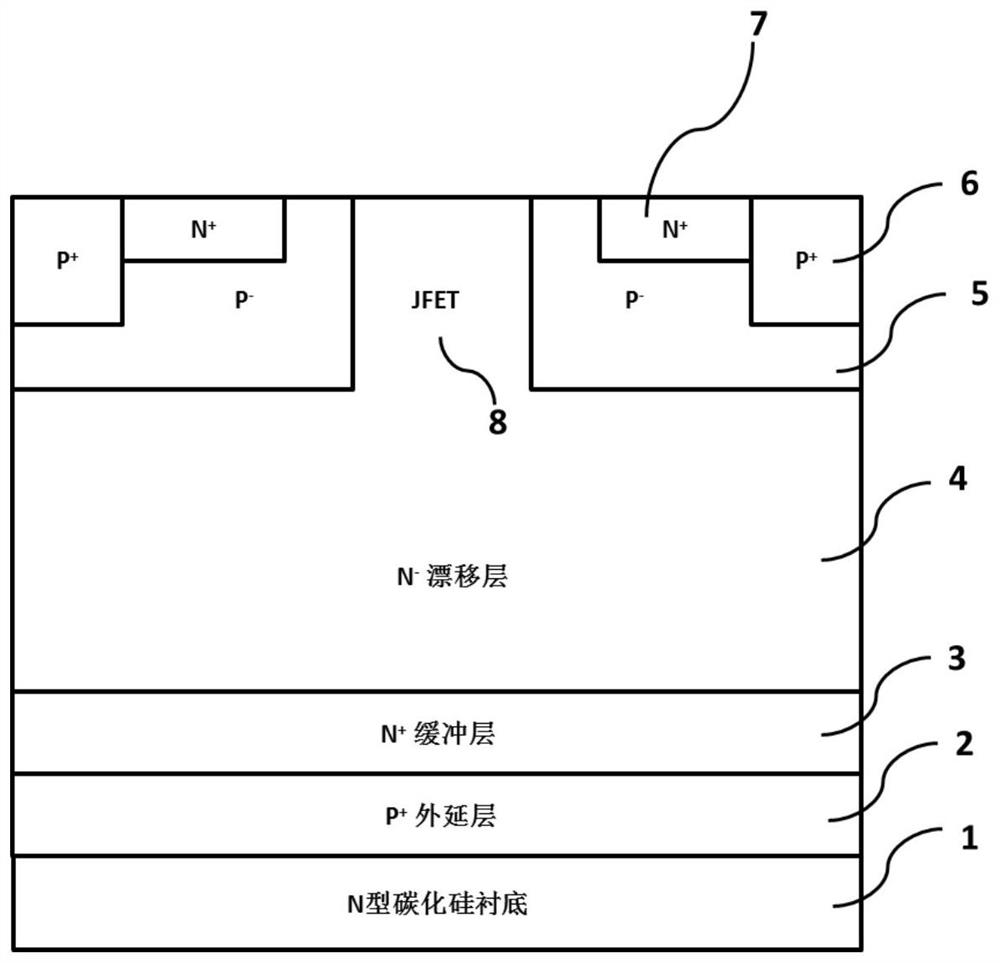

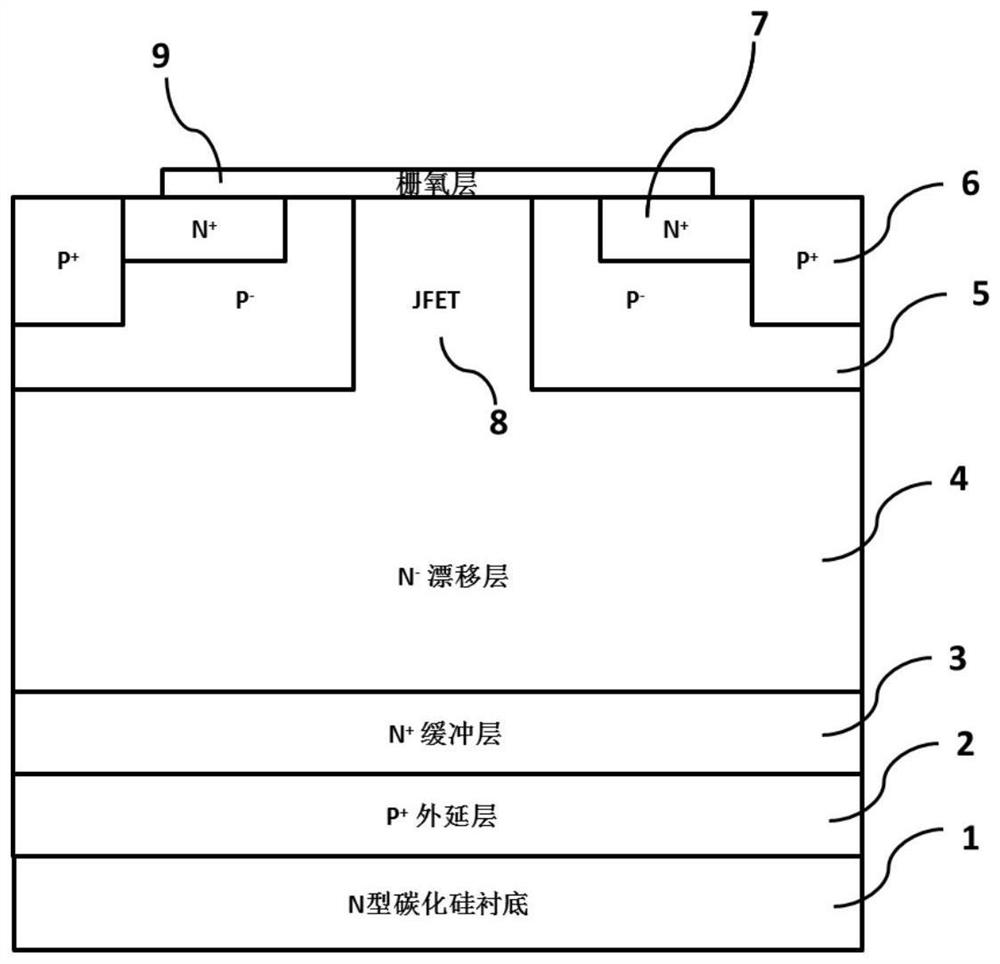

[0039] The technical solutions of the present invention will be further described below in conjunction with the accompanying drawings and embodiments.

[0040] The invention provides a method for preparing an N-channel silicon carbide bipolar device by using an N-type silicon carbide substrate to grow epitaxy, through a high-temperature oxidation process, a front-side MOS preparation process, a back-side thinning process, and a laser annealing process. The specific process Proceed as follows:

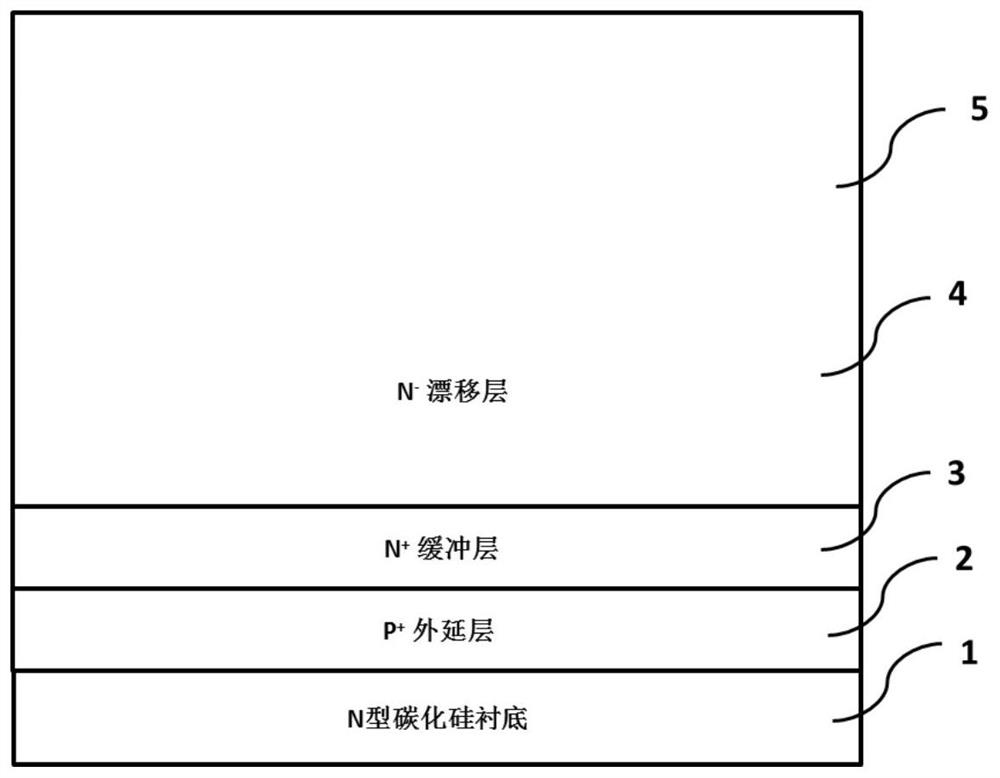

[0041] Step 1, growing P sequentially on the N-type silicon carbide substrate 1 + Epitaxial layer 2, N + Buffer 3 and N - Drift layer 4, such as figure 1 shown. First, epitaxially grow P on the N-type silicon carbide substrate 1 + Epitaxial layer 2, P-type doping concentration is 1e18cm -3 ~1e20cm -3, the thickness is 3μm~30μm; secondly, in P + Epitaxial growth of N on the epitaxial layer 2 + Buffer layer 3, N-type doping concentration is 3e16cm -3 ~3e18cm -3 , the thickness ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More