Silicon carbide power device and preparation method thereof

A technology of power devices and silicon carbide, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of low device channel mobility and large on-resistance, and achieve improved channel mobility and channel The effect of track density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

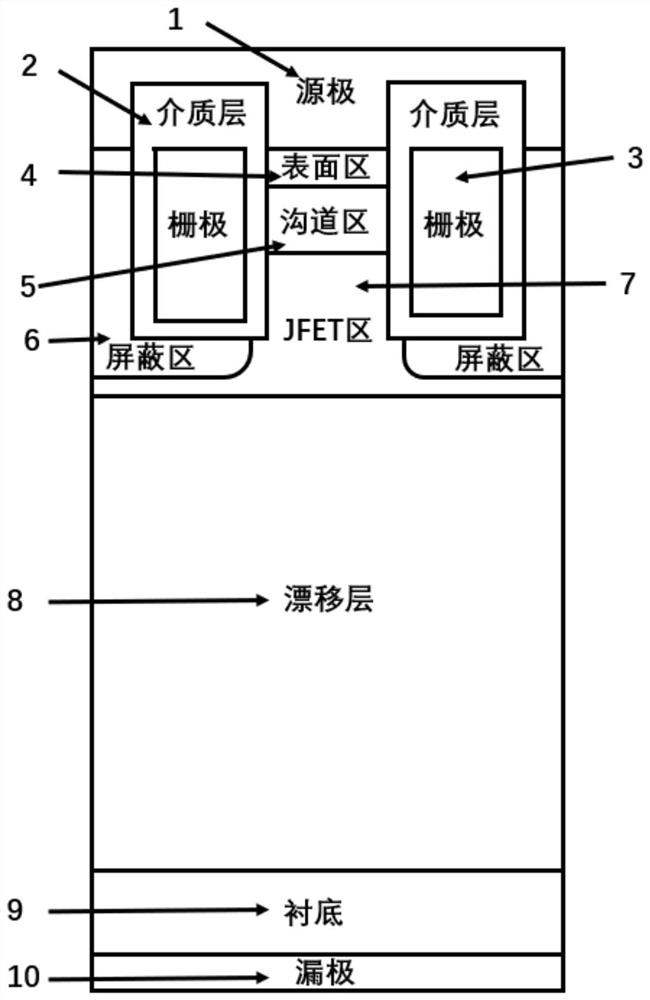

[0057] The structure of the SiC power device prepared in this embodiment is as follows figure 1 As shown, it includes the substrate 9 required for epitaxy (in order to form ohmic contact with the electrode, it needs to be heavily doped), the drift layer 8 as a withstand voltage structure, the shielding region 6 for shielding the high electric field at the bottom of the gate dielectric layer, and the middle of the shielding region 6 Appropriately doped to reduce the JFET region 7 of the on-resistance, the surface in contact with the gate 3 produces the channel region 5 of the channel inversion layer when the device is turned on, and the heavy doping between the channel region 5 and the electrode (for the same purpose Ohmic contact) surface region 4, contact electrodes such as gate 3, drain 10, source 1, etc., gate dielectric layer 2 around gate 3, and passivation layer, field plate, etc. necessary in traditional SiC power devices Although the structures are not shown in the fig...

Embodiment 2

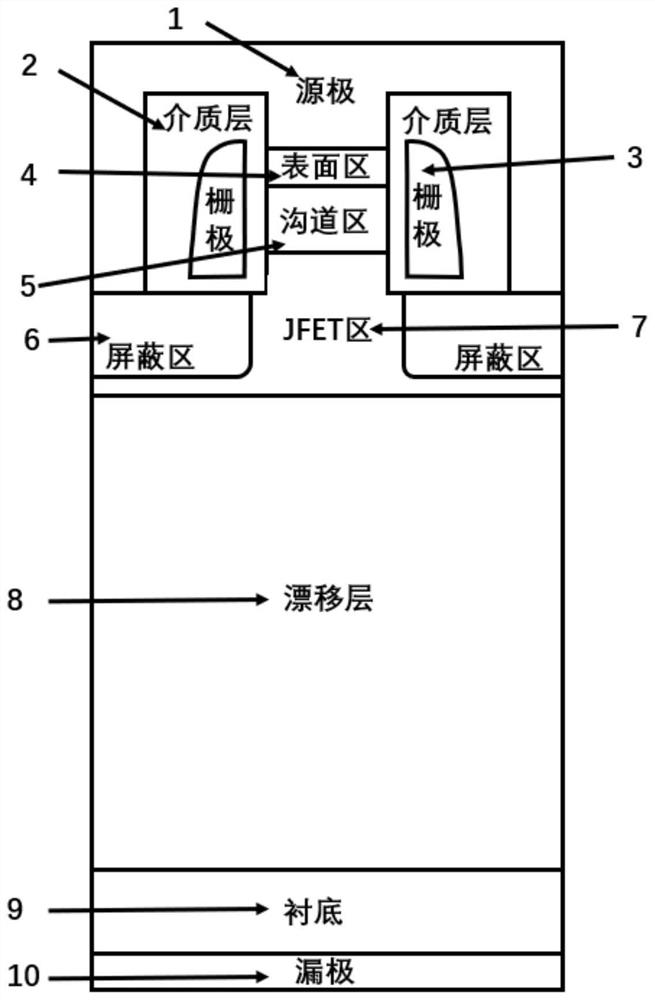

[0071] The structure of the SiC power device prepared in this embodiment is as follows figure 2 shown, with figure 1 The difference of the structure shown is that the shielding region 6 is changed from surrounding the gate 3 to being at the bottom of the gate 3 .

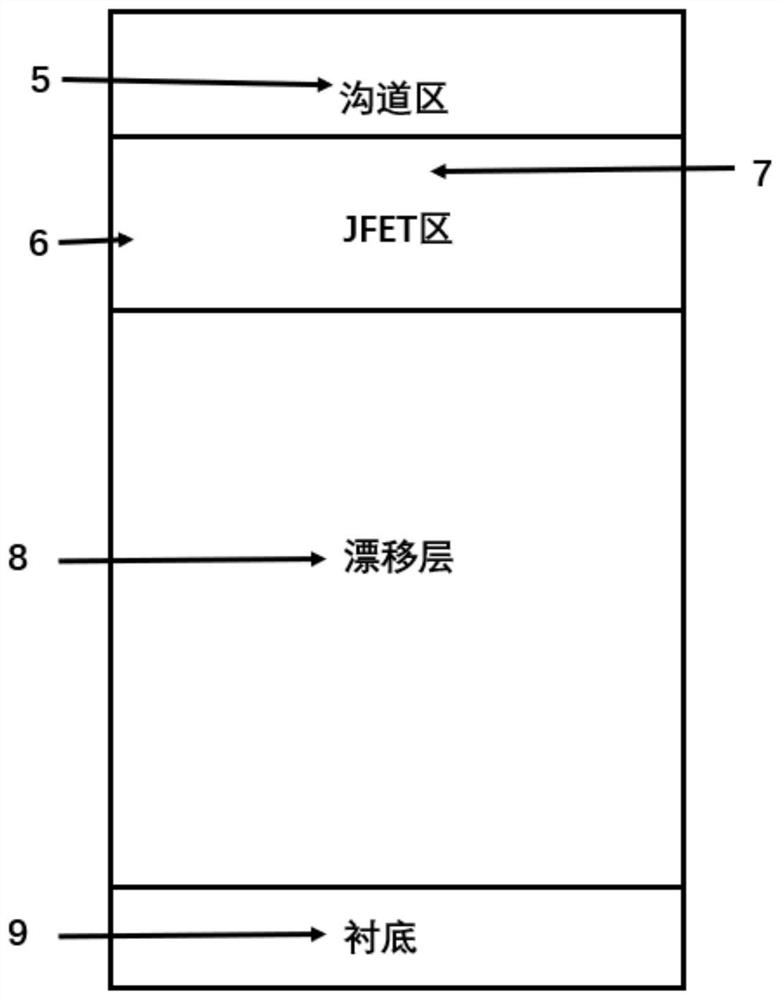

[0072] Step 1. First select N + type silicon carbide substrate 9, on which epitaxially grow N - Type drift layer 8, N-type JFET region 7, channel region 5 and surface region 4, such as Figure 8 shown;

[0073] The thickness is selected as 350 μm, and the doping concentration of phosphorus ions is 5×10 19 cm -3 N + Type SiC substrate 9, cleaned, vapor phase epitaxial growth thickness of 10 μm, phosphorus ion doping concentration of 8×10 15 cm -3 N - The drift layer 8 has a thickness of 3 μm and a phosphorus ion doping concentration of 3×1016 cm -3 The N-type JFET region 7 has a thickness of 0.5 μm and an aluminum ion doping concentration of 1E16cm -3 (or 8E15cm -3 ) of the channel region 5 (so that the ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More