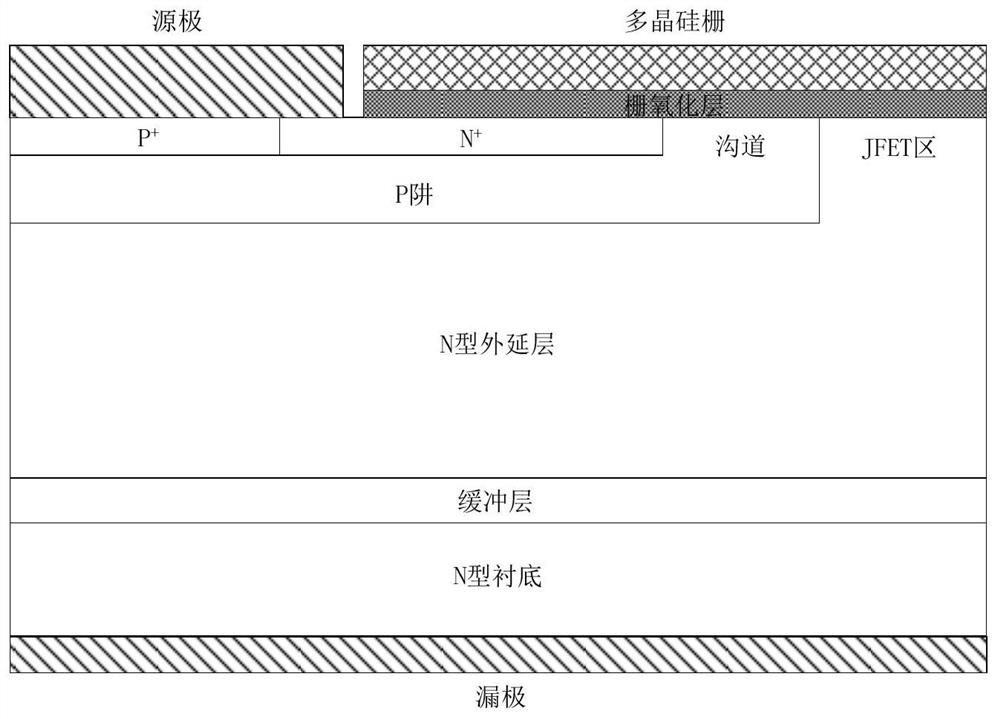

Silicon carbide MOSFET device and preparation method thereof

A technology of silicon carbide and silicon carbide substrates, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., to achieve high channel carrier mobility, improve channel current capability, and reduce JFET area resistance Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] Below in conjunction with accompanying drawing and specific embodiment, technical solution of the present invention is described further in detail:

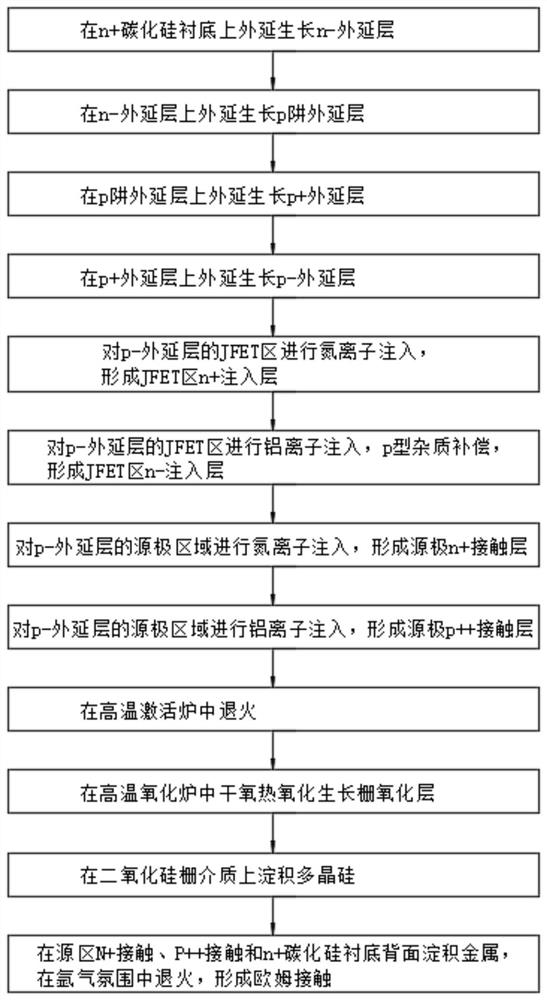

[0040] Please also refer to Figure 2-Figure 3k , the preparation method of the silicon carbide MOSFET device provided in this embodiment, comprises the following steps:

[0042] Step 1, epitaxial growth on n+ silicon carbide substrate with a doping concentration of 1e15cm -3 ~9e15cm -3 , an n-epitaxial layer with a thickness of 8-50 μm; as Figure 3a shown;

[0043] Step 2, epitaxial growth on the n- epitaxial layer with a doping concentration of 4e16cm -3 ~8e16cm -3 , a p-well epitaxial layer with a thickness of 0.5-0.7 μm; such as Figure 3b shown;

[0044] Step 3, epitaxial growth on the p-well epitaxial layer with a doping concentration of 3e18cm -3 ~7e18cm -3 , a p+ epitaxial layer with a thickness of 0.3-0.4 μm; such as Figure 3c shown;

[0045] Step 4, epitaxial growth on the p+ epitaxial layer with a...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More