Manufacture method of semiconductor device

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as lowering product yield, semiconductor device failure, and corrosion of the first oxide layer 130a, so as to ensure quality and speed up Etching rate, the effect of improving electrical properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

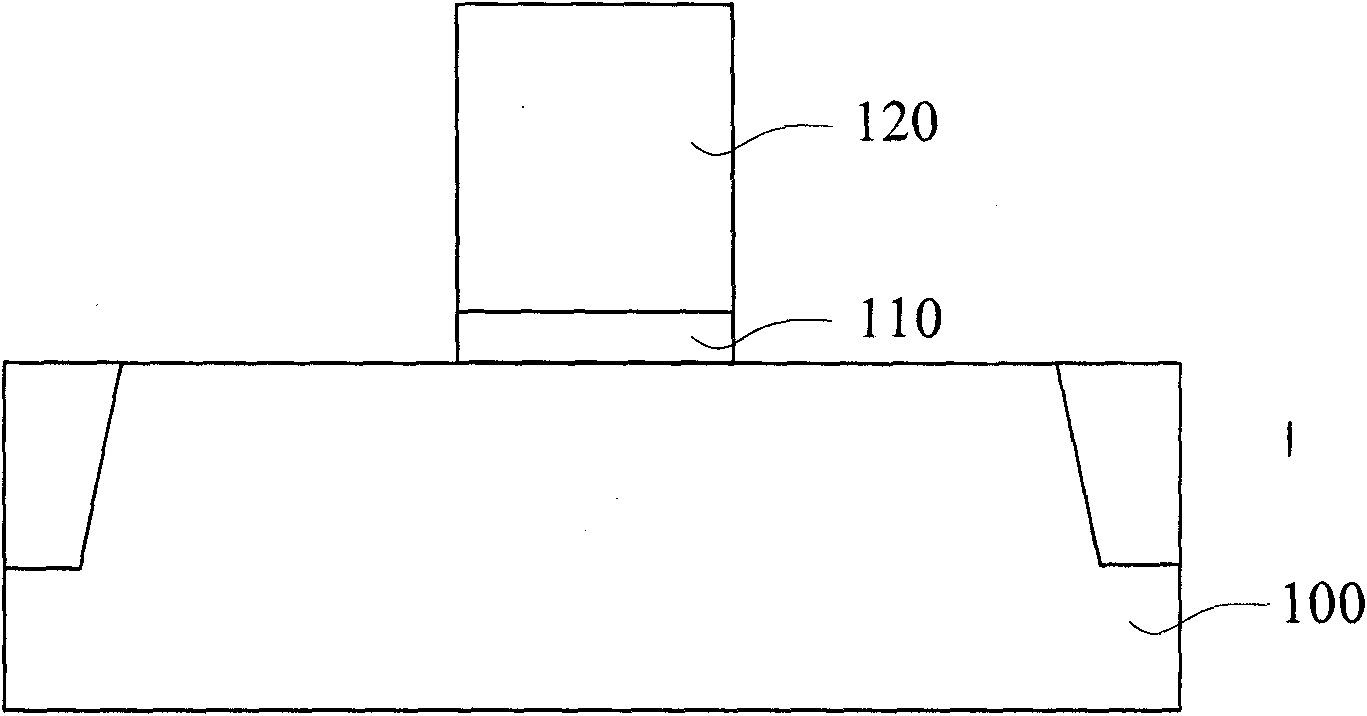

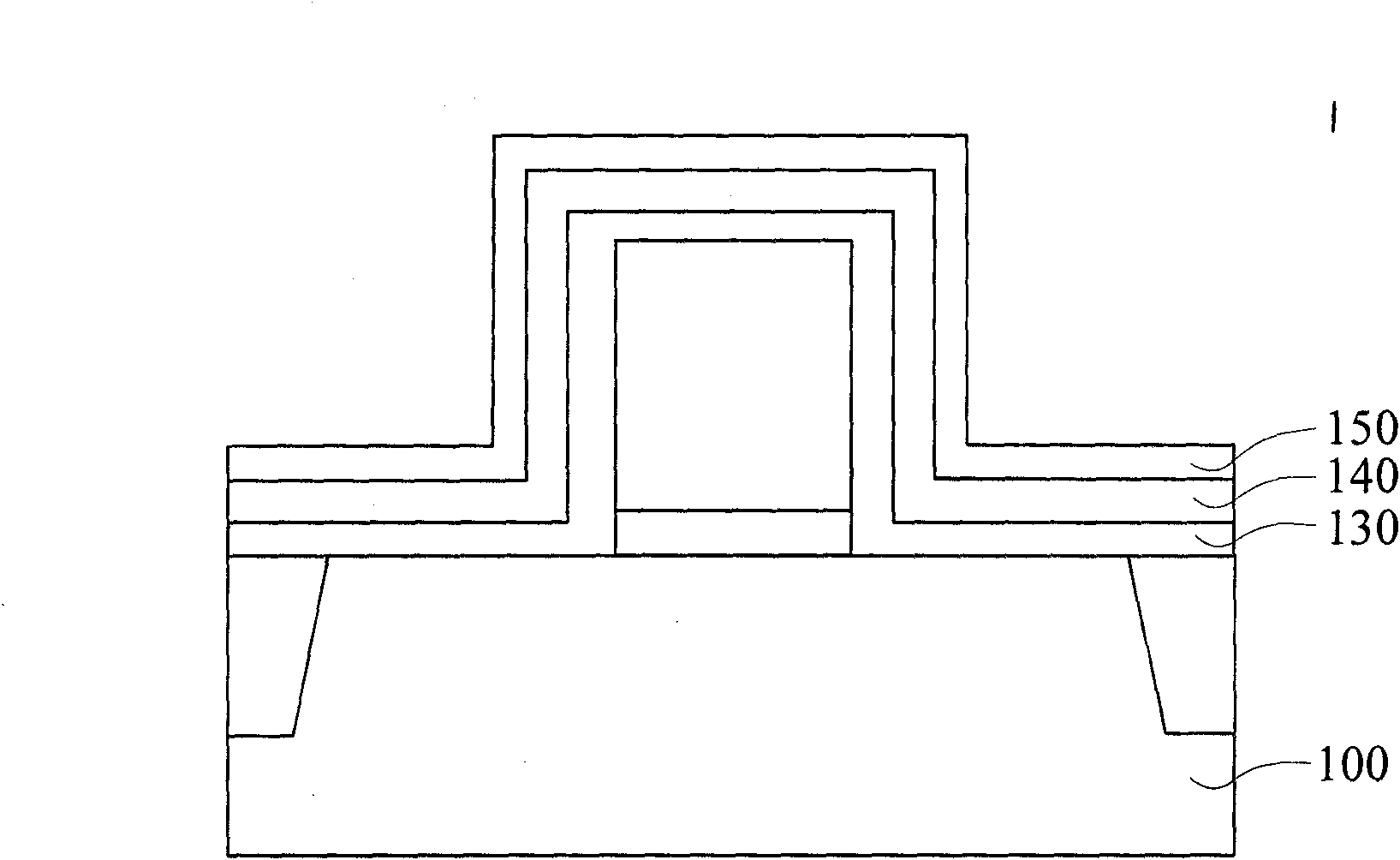

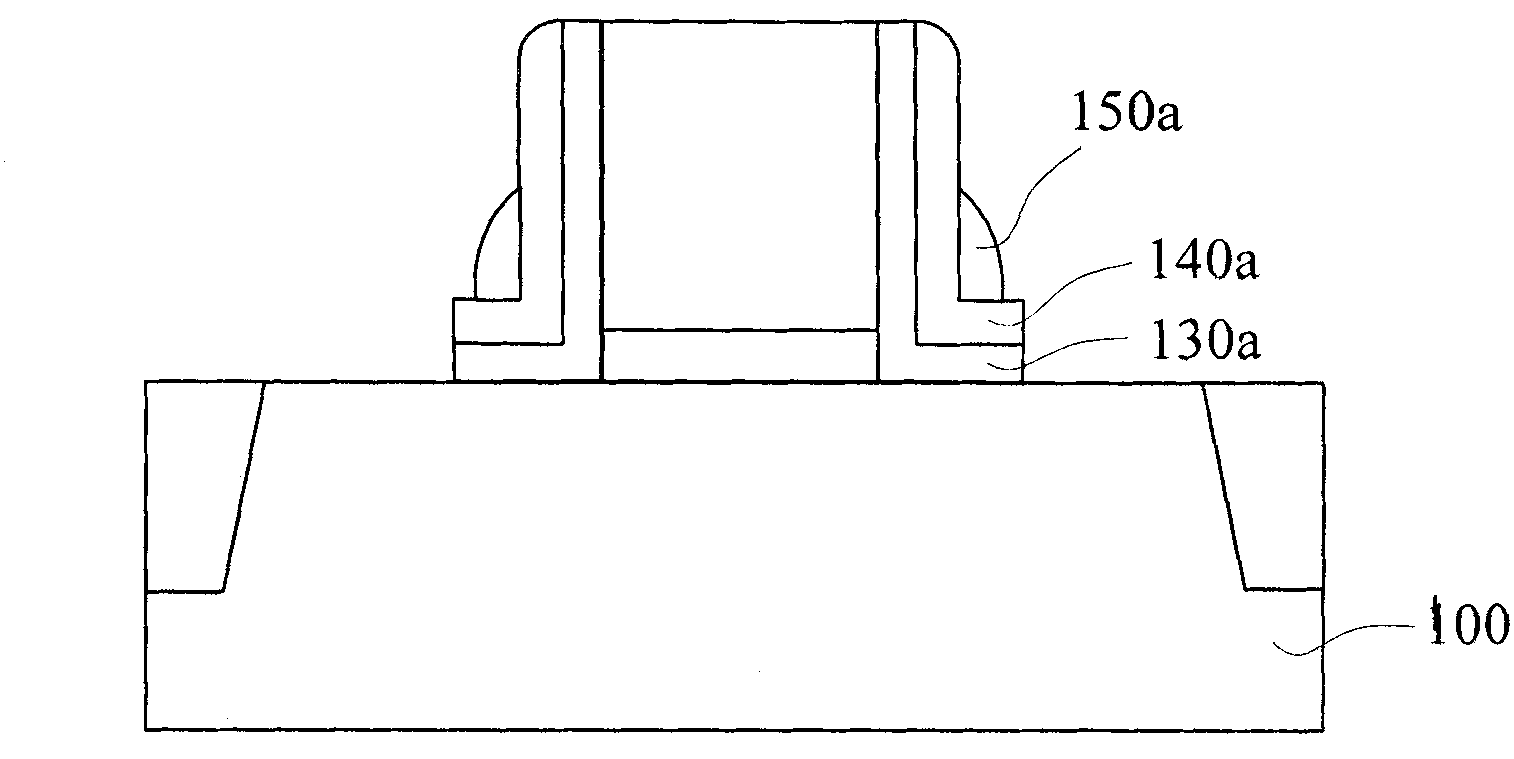

[0027] The core idea of the present invention is to provide a manufacturing method of a semiconductor device. In the method, after forming the sidewall layer and before performing the wet etching process, the process step of argon ion implantation is added. The argon ion implantation process will make the sidewall layer The remaining second oxide layer at the corner of the wall layer is amorphized, thereby accelerating the etching rate of the second oxide layer in the wet etching process, ensuring that the remaining second oxide layer at the corner of the side wall layer is completely removed, and ensuring the final formation The quality of self-aligned metal silicide, thereby improving the electrical performance of semiconductor devices.

[0028] Please refer to figure 2 , which is a flow chart of a method for manufacturing a semiconductor device provided by an embodiment of the present invention. In combination with this figure, the method includes the following steps:

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More