N-InP-based monolithic integrated optical logic gate and manufacturing method thereof

A monolithic integration, optical logic technology, applied in the direction of logic circuits using optoelectronic devices, logic circuits using specific components, logic circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

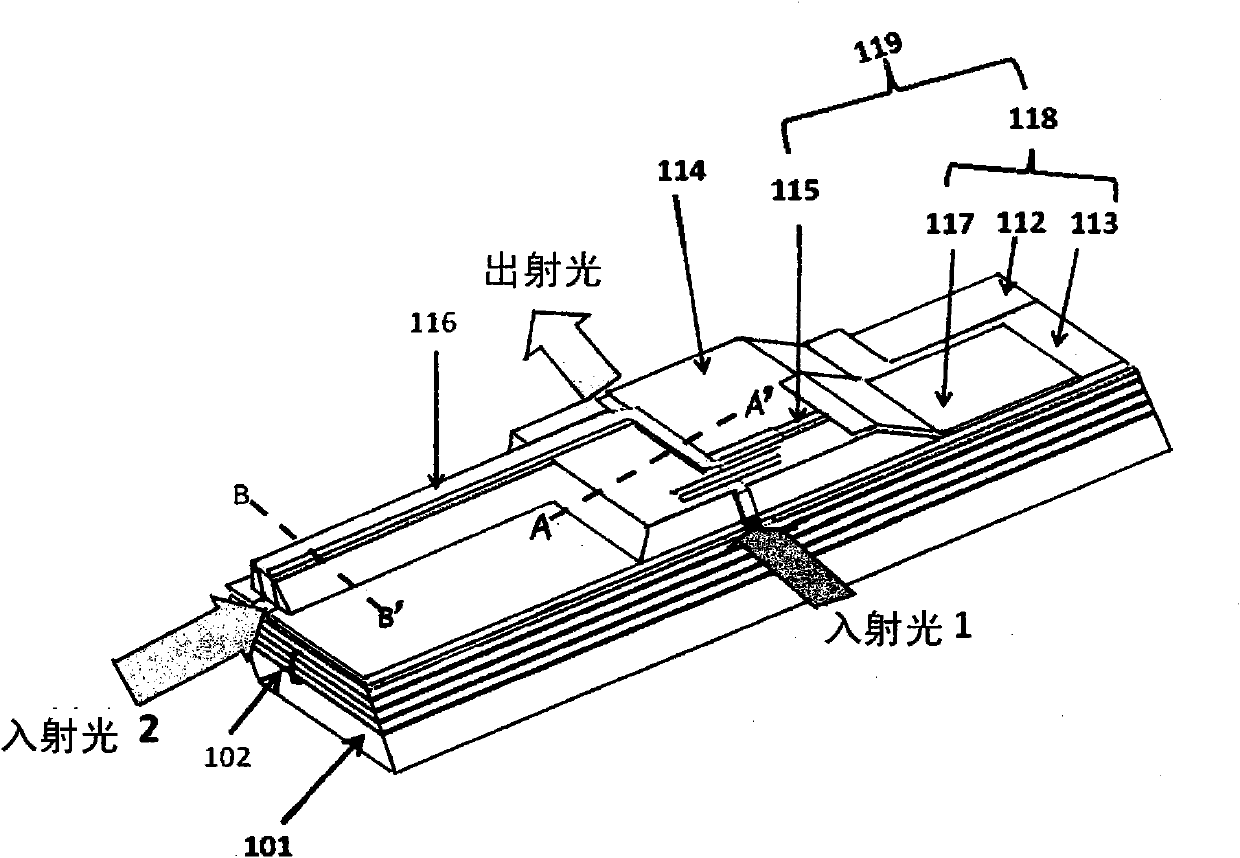

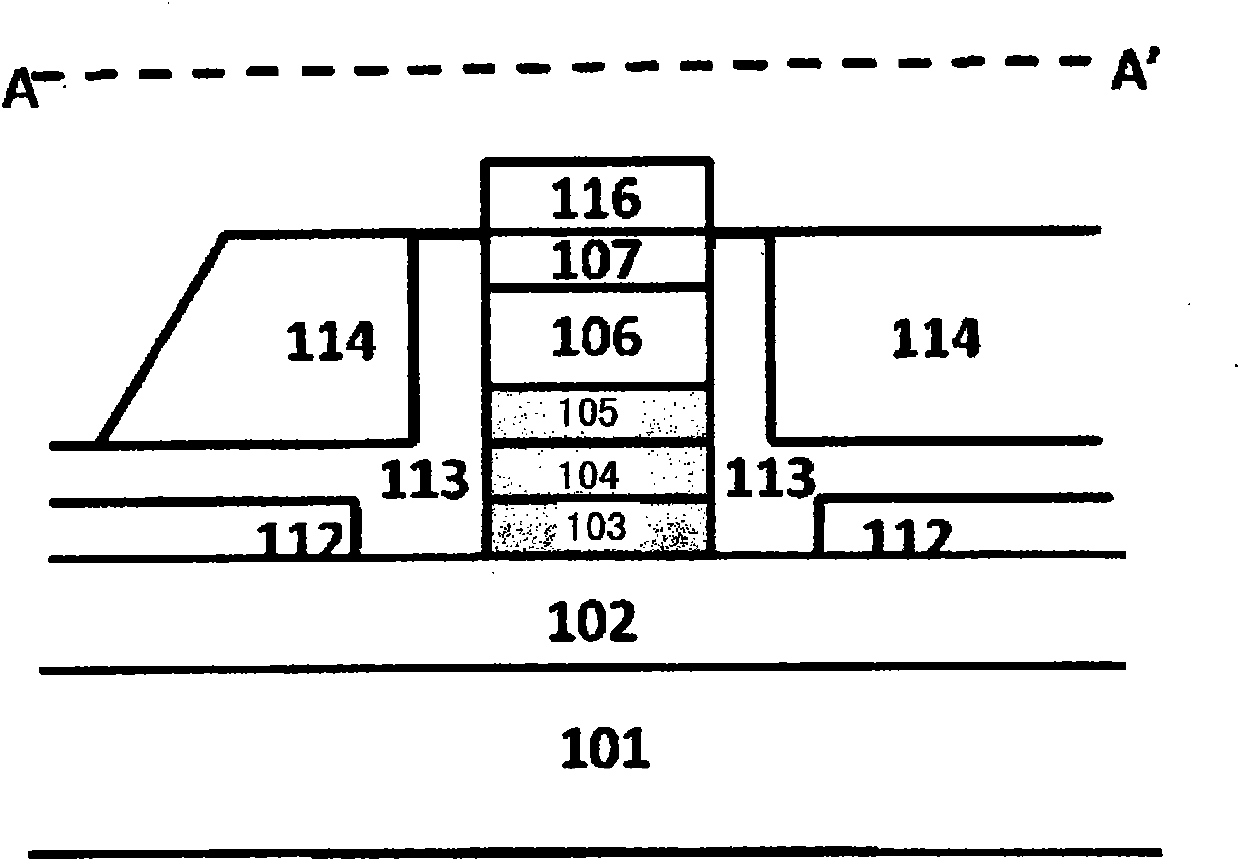

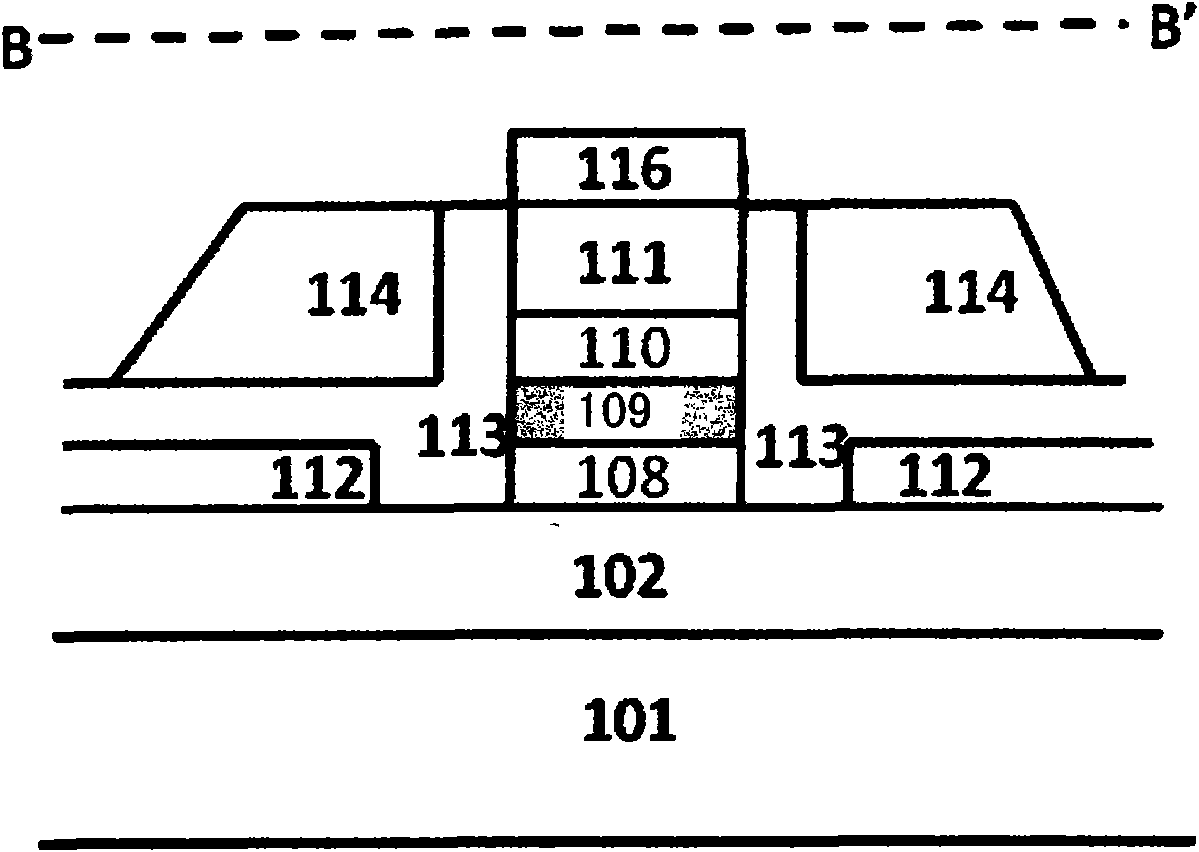

[0014] see Figure 1A -C, the present invention is based on n-InP monolithically integrated optical logic gate, comprising:

[0015] A substrate 101, which is an n-type (100) InP substrate, such as Figure 1A shown;

[0016] An n-type diluted waveguide layer 102. The n-type diluted waveguide layer 102 is fabricated on the substrate 101. The n-type diluted waveguide layer 102 is composed of 5-10 cycles of InP layers and InGaAsP layers alternately, and the doping concentration is 1×10 18 cm -3 ; wherein the bandgap wavelength of the InGaAsP layer is between 1.1-1.3 μm, which matches the lattice constant of the InP substrate; the total thickness of the diluted waveguide layer 102 is 1.5-4 μm, and the introduction of the diluted waveguide layer 102 can greatly improve the fiber- The coupling efficiency of the waveguide.

[0017] An undoped InGaAsP lower confinement layer 103, an undoped multi-quantum well layer 104, an undoped InGaAsP upper confinement layer 105, a p-type heavi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| wavelength | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| wavelength | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More