Preparation method of crystalline silicon solar cell

A solar cell, crystalline silicon technology, applied in circuits, electrical components, semiconductor devices, etc., can solve the problems of the decline of the life of the minority carrier, the inability to form ohmic contacts, the warpage of difficult crystalline silicon solar cells, etc., to improve absorption, increase Back passivation effect, the effect of reducing the impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

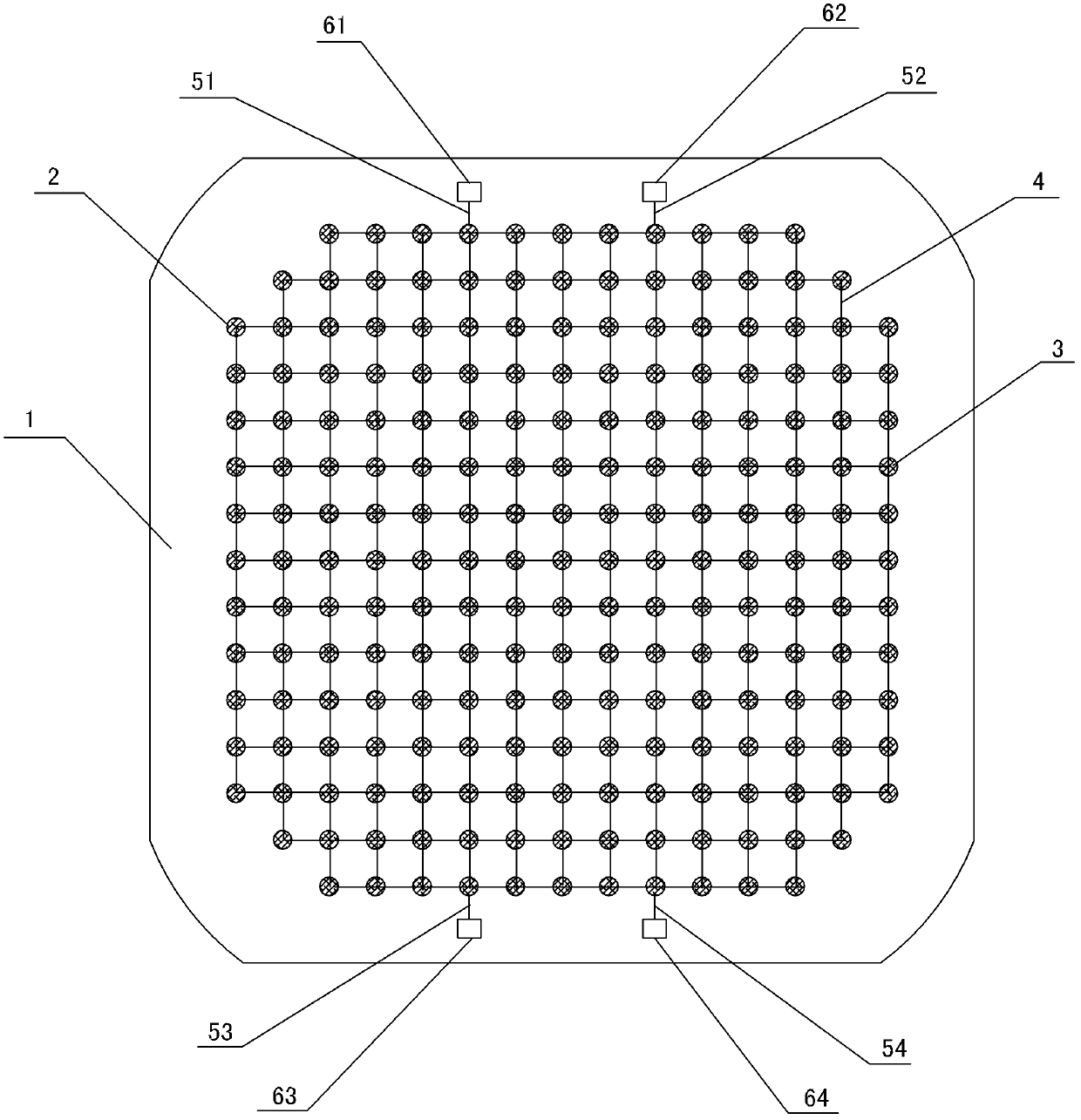

Image

Examples

Embodiment 1

[0026] A method for preparing a crystalline silicon solar cell proposed by the present invention is divided into the following steps according to the production sequence of the process line: making texture on the silicon wafer; diffusing on the silicon wafer to make a PN junction; performing deedge junction treatment on the silicon wafer; Passivate the surface of the silicon wafer; make front and back electrodes; sinter.

[0027] In this specific embodiment, conventional processes are used for texturizing the silicon wafer, making PN junctions by diffusion on the silicon wafer, deedge-junctioning the silicon wafer, fabricating front electrodes and sintering.

[0028] In this specific example, a 13.56MHz plasma-enhanced chemical vapor deposition (PECVD, Plasma Enhanced Chemical Vapor Deposition) process is used to perform double-sided passivation treatment on both surfaces of the silicon wafer, and the specific treatment process is as follows:

[0029]1) A 13.56MHz plasma-enhan...

Embodiment 2

[0046] This embodiment is basically the same as the first embodiment, except that the process conditions used to passivate the surface of the silicon wafer are different.

[0047] In this embodiment, the specific process conditions for coating aluminum oxide film are: power is 3000W, vacuum degree is 1.8 Torr, flow rate of high-purity oxygen is 3.7 liters / minute, flow rate of trimethylaluminum is 0.42 liters / minute, substrate The temperature is 500°C, the deposition time is determined by the speed of depositing aluminum oxide film, the thickness of aluminum oxide film is 50nm; the specific process conditions of front passivation are: power is 2500W, vacuum degree is 1.7 torr, high-purity ammonia gas flow rate is 4 liters per minute, the substrate temperature is 420°C, and the passivation time is 4 minutes; the specific process conditions for plating silicon nitride films are: power 3500W, vacuum degree 1.5 Torr, high-purity ammonia flow rate 7 liters / minutes, the silane flow ...

Embodiment 3

[0049] This embodiment is basically the same as the first embodiment, except that the process conditions used to passivate the surface of the silicon wafer are different.

[0050] In this embodiment, the specific process conditions for coating the aluminum oxide film are: the power is 3000W, the vacuum degree is 1.5 Torr, the flow rate of high-purity oxygen is 4.5 liters / minute, the flow rate of trimethyl aluminum is 0.47 liters / minute, the substrate The temperature is 470°C, the deposition time is determined by the speed of depositing aluminum oxide film, the thickness of aluminum oxide film is 170nm; the specific process conditions of front passivation are: power is 2500W, vacuum degree is 1.8 torr, high-purity ammonia gas flow rate is 6 liters per minute, the substrate temperature is 480°C, and the passivation time is 3.5 minutes; the specific process conditions for plating silicon nitride films are: power 3500W, vacuum degree 1.8 Torr, high-purity ammonia flow rate 3.5 lite...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More