Integrated circuit copper interconnection structure and preparation method thereof

A technology of copper interconnection structure and integrated circuit, which is applied in the field of microelectronics, can solve the problems such as the increase of characteristic aspect ratio, and achieve the effect of improving conductivity, reducing thickness and reducing resistivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

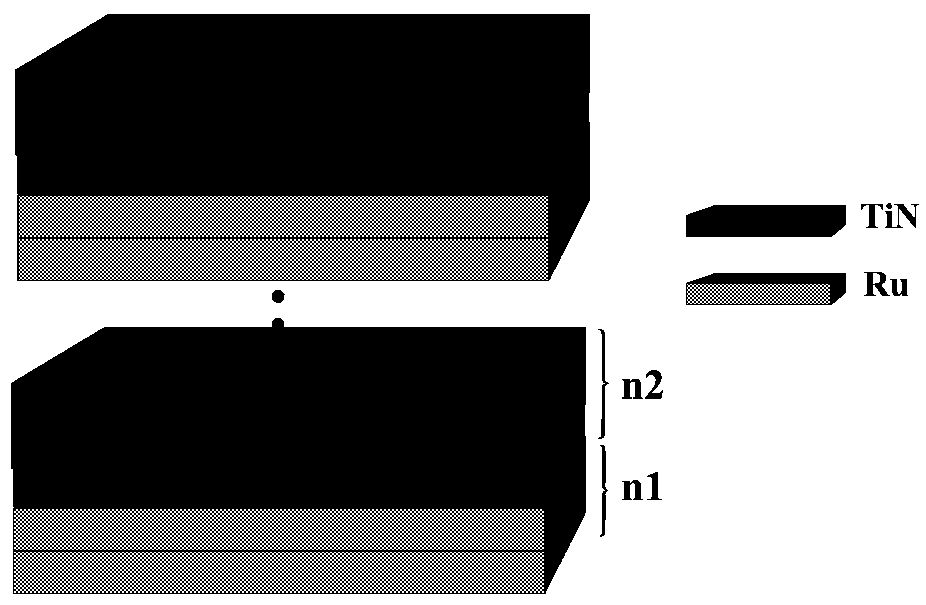

[0031] The basic idea of the present invention is to use the ALD method to grow the overlapping structure of TiN and Ru atomic layers to form a Ru-N-Ti composite structure instead of the traditional TaN / Ta as the Cu diffusion barrier layer / adhesion layer / seed layer.

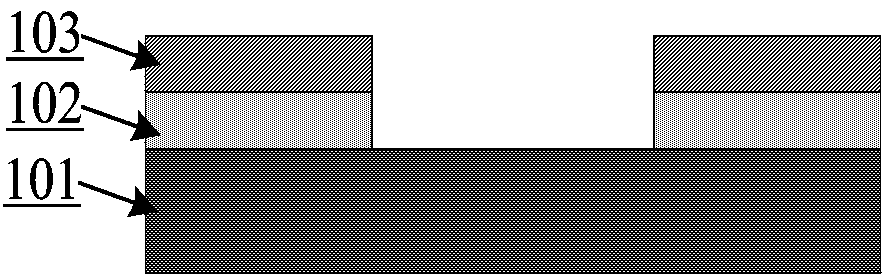

[0032] refer to figure 1 , using standard cleaning SC-1, SC-2 solution, 1:20 diluted hydrofluoric acid and deionized water to clean the Si substrate in sequence to remove impurities and natural oxide layer, and use high-purity N 2 blow dry. On the cleaned Si substrate (101), deposit the etch stop layer silicon nitride (102) and the dielectric layer SiO for interlayer insulation in sequence. 2 (103). The trenches or vias for the interconnect structure are formed using standard photolithography and etching processes.

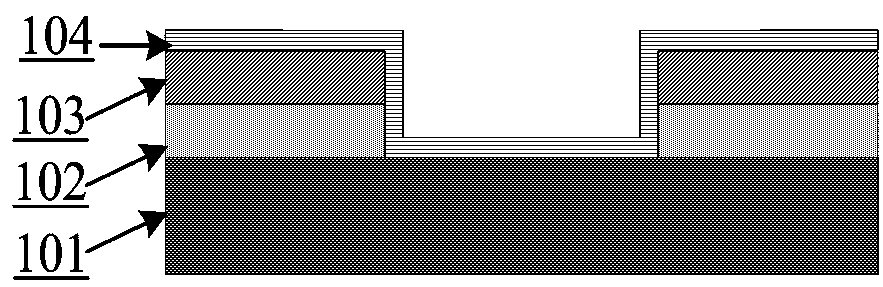

[0033] refer to figure 2 , growing Ru-N-Ti films on the trenches using PEALD technique (104). The TiN growth source is TDEAT and NH 3 Gas plasma, Ru growth source is Ru(Cp) 2 and O 2 plasm...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com