Planar indium gallium arsenic photosensitive chip with improved surface passivation and preparation method thereof

An indium gallium arsenic, planar technology, applied in the direction of final product manufacturing, sustainable manufacturing/processing, electrical components, etc., can solve the problems of reduced surface passivation, surface damage of epitaxial materials, InP surface oxidation, etc., to achieve enhanced passivation chemical effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The specific implementation method of the present invention will be described in detail below in conjunction with the accompanying drawings.

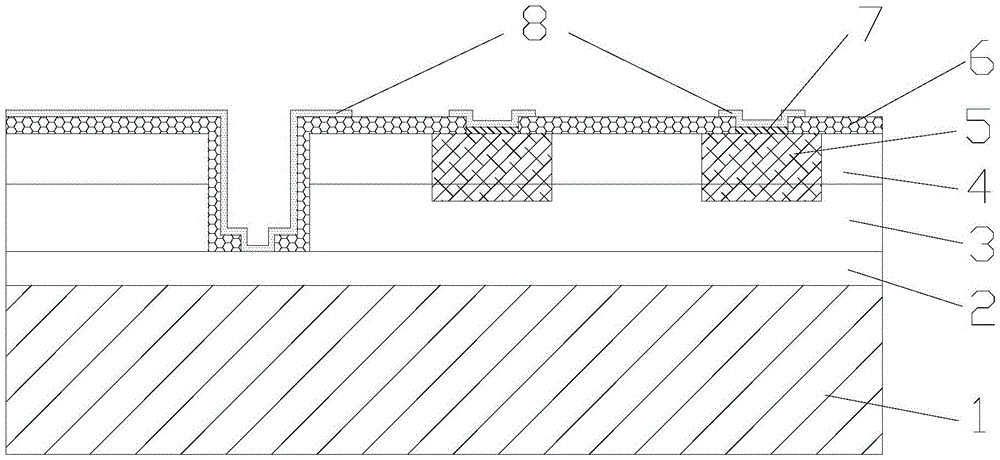

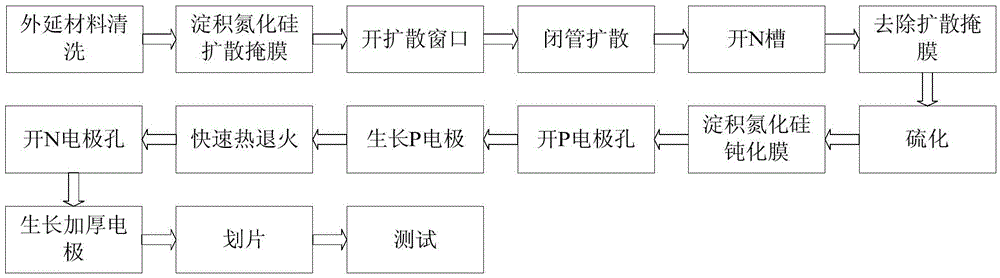

[0046] as attached figure 1 As shown, the epitaxial wafer used in this embodiment adopts metal-organic chemical vapor deposition (MOCVD) technology, and on a semi-insulating InP substrate 1 with a thickness of 350 μm, an N-type InP layer 2 with a thickness of 0.5 μm is sequentially grown. Fluor concentration>2×10 18 cm -3 ; InGaAs intrinsic absorption layer 3 with a thickness of 2.5 μm and a carrier concentration of 5×10 16 cm -3 ; An N-type InP cap layer 4 with a thickness of 1 μm and a carrier concentration of 5×10 16 cm -3 . The preparation process of the planar InGaAs infrared detector chip in this embodiment is based on the existing process, after the closed-tube diffusion, the process of adding nitrogen atmosphere heat treatment; before depositing the silicon nitride passivation film, introducing The process of remov...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More