Ion implantation doping-based preparation method of hafnium oxide ferroelectric gate

An ion implantation and ferroelectric technology, which is applied in the manufacture of circuits, electrical components, semiconductors/solid-state devices, etc., can solve the problems of demanding heating chamber temperature and reaction gas, increasing experimental costs, process steps, and difficulty in controlling the properties of deposited films, etc. , to achieve the effects of reducing interface effects, controllable performance, and precise depth control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The following examples will further illustrate the present invention in conjunction with specific accompanying drawings:

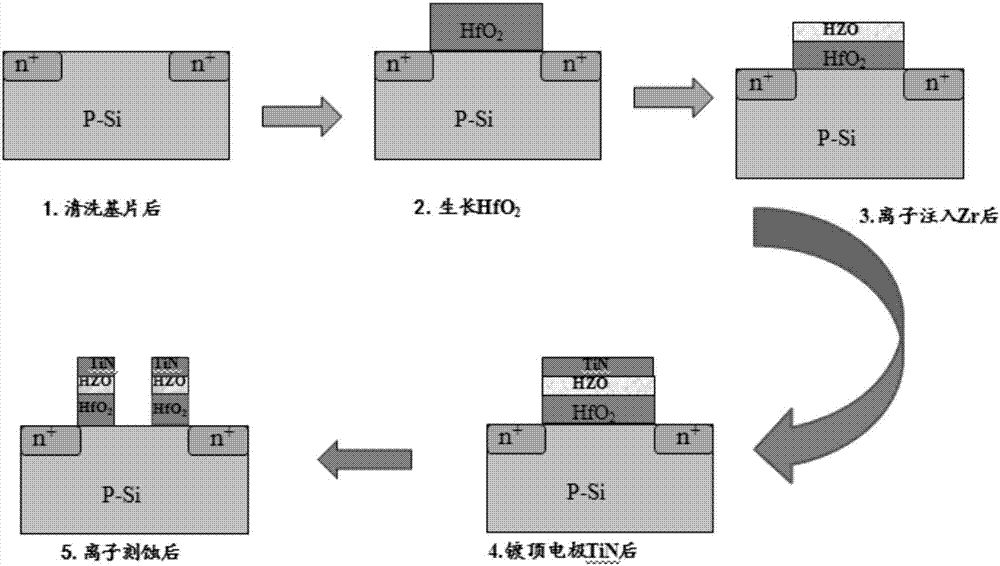

[0025] see figure 1 It is a flow chart of the preparation process of MFIS ferroelectric gate based on ion implantation doping HfO2.

[0026] 1. Take P-Si(100) and clean it with HF to remove the silicon oxide on the surface;

[0027] 2. Use ALD to grow 22nm HfO2 on the silicon wafer as a buffer layer;

[0028] 3. Use ion implantation technology to dope hafnium oxide with Zr to a depth of 11nm, then anneal the ion-implanted sample in oxygen in a rapid annealing furnace, the annealing temperature is 550°C, and the annealing time is 30s;

[0029] 4. Plating 15nm top electrode TiN on the HZO film by CVD, followed by annealing in nitrogen, the annealing temperature is 450°C. Annealing time 30s.

[0030] 5. Finally, perform plasma etching on the MFIS film structure, using argon plasma, chlorine gas plasma, ion beam incident angle 60°, argon ion beam de...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More