N-Ge-i-Ge-p-Si structural waveguide-type photoelectric detector based on LRC technology and manufacturing method

A photodetector, n-ge-i-ge-p-si technology, used in semiconductor devices, circuits, electrical components, etc., can solve the problems of poor thermal conductivity and mechanical properties, poor compatibility, limited application, etc. Low thermal budget, short process cycle time, and the effect of reducing dark current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

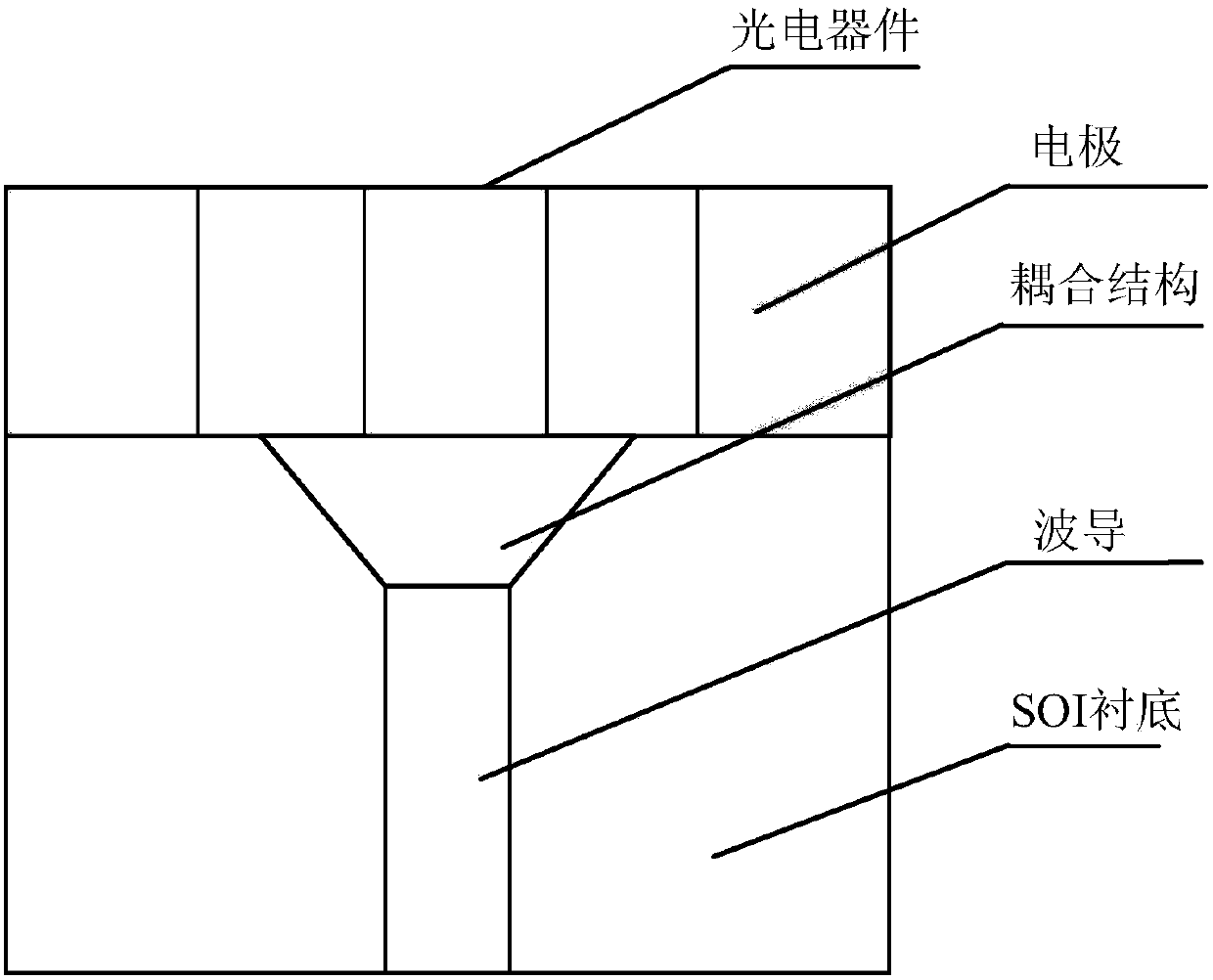

[0046] See figure 1 , figure 1 It is a schematic top view of an n-Ge-i-Ge-p-Si structure waveguide photodetector based on the LRC process provided by an embodiment of the present invention. The photodetector includes an SOI substrate and a waveguide, a coupling structure and a device part arranged on the top Si layer of the SOI substrate. The device part is finally formed into a photoelectric device through a semiconductor process to form a waveguide type photodetector.

[0047] It should be noted that the epitaxial Ge semiconductor material on the Si substrate is not only fully compatible with the existing Si process, but also has good response characteristics to the C-band (1528-1560 nm) optical signal in optical communication, and is applied to Si-based The photoelectric integration technology has great potential. At the same time, if the Ge PiN photodetector has a waveguide structure, because the light transmission and absorption are along the waveguide direction, and the car...

Embodiment 2

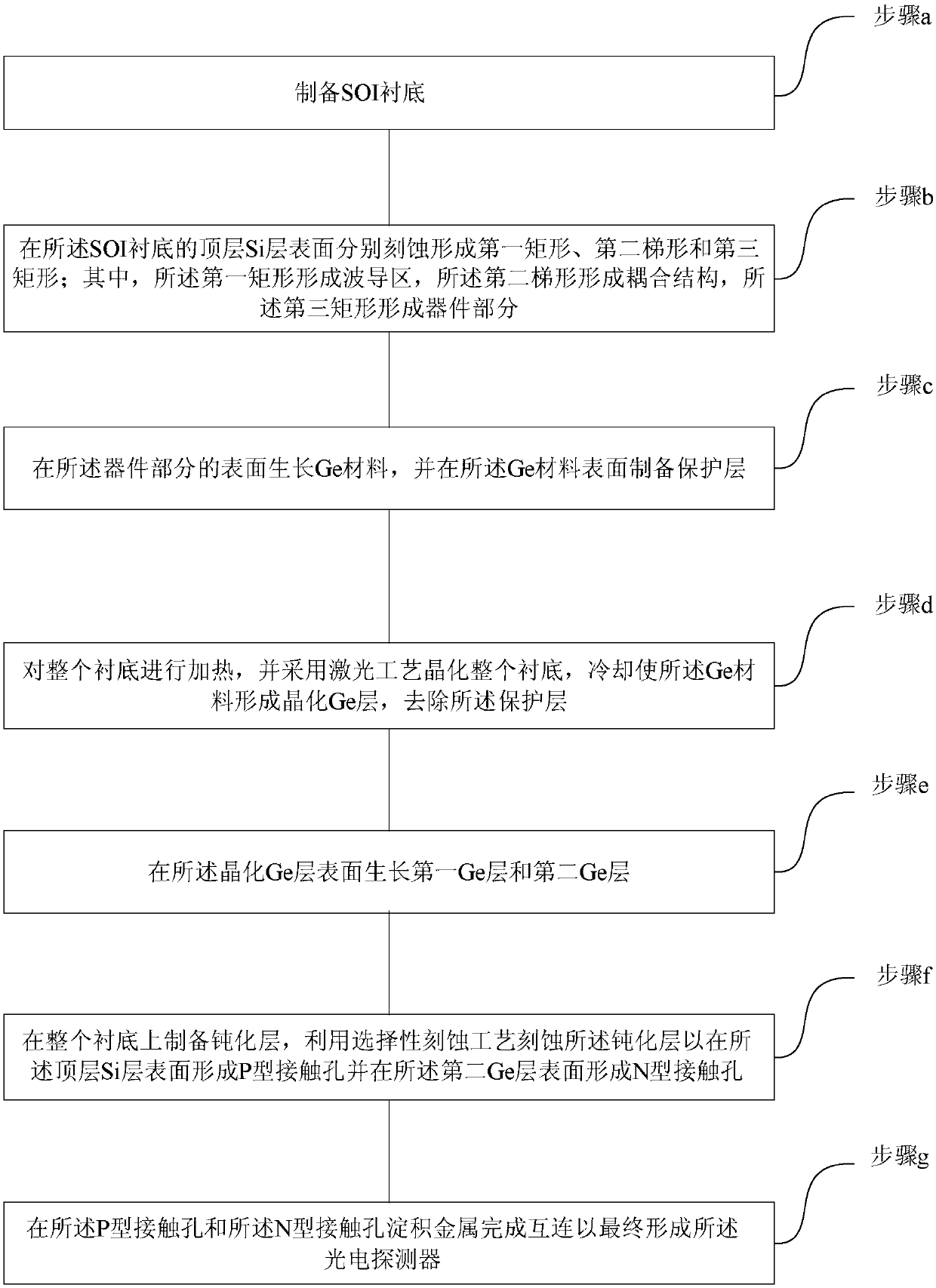

[0080] See also Figure 3a-Figure 3k , Figure 3a-Figure 3k It is a schematic diagram of a manufacturing method of an n-Ge-i-Ge-p-Si structure waveguide photodetector based on the LRC process provided by an embodiment of the present invention. In this embodiment, on the basis of the foregoing embodiment, the preparation method of the n-Ge-i-Ge-p-Si structure waveguide photodetector based on the LRC process of the present invention is described in detail as follows:

[0081] S101. The substrate is selected. Such as Figure 3a As shown, a single crystal silicon (Si) substrate sheet (001) is selected as the initial material 101;

[0082] S102, SOI substrate preparation. Such as Figure 3b As shown, choose O + The dose is 1.8×10 18 cm -2 Perform oxygen injection isolation, and then high-temperature annealing to form 1μm thick SiO 2 The SOI substrate with layer 102 and Si layer 103 of 1.5 μm thick.

[0083] S103. Preparation of waveguide and coupling region. Selectively etch to form a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More