Micron-sized diode chip and preparation method

A diode and micron-level technology, applied in electrical components, circuits, semiconductor devices, etc., can solve problems such as increased sidewall defects, reduced quantum efficiency in devices, and limitations in communication distance and practicability of micron LEDs, and achieve high output optical power , the effect of high response current and detection sensitivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

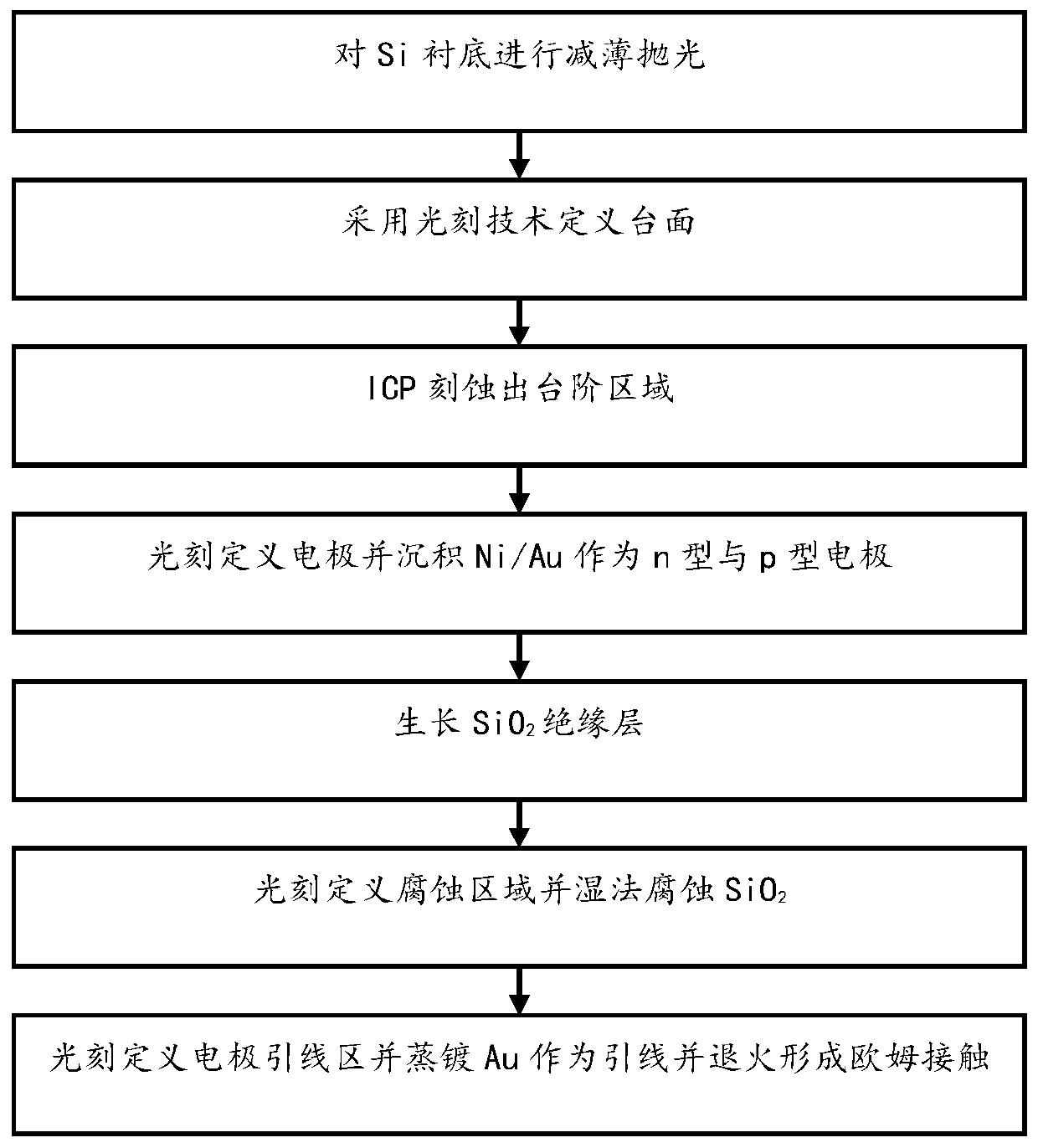

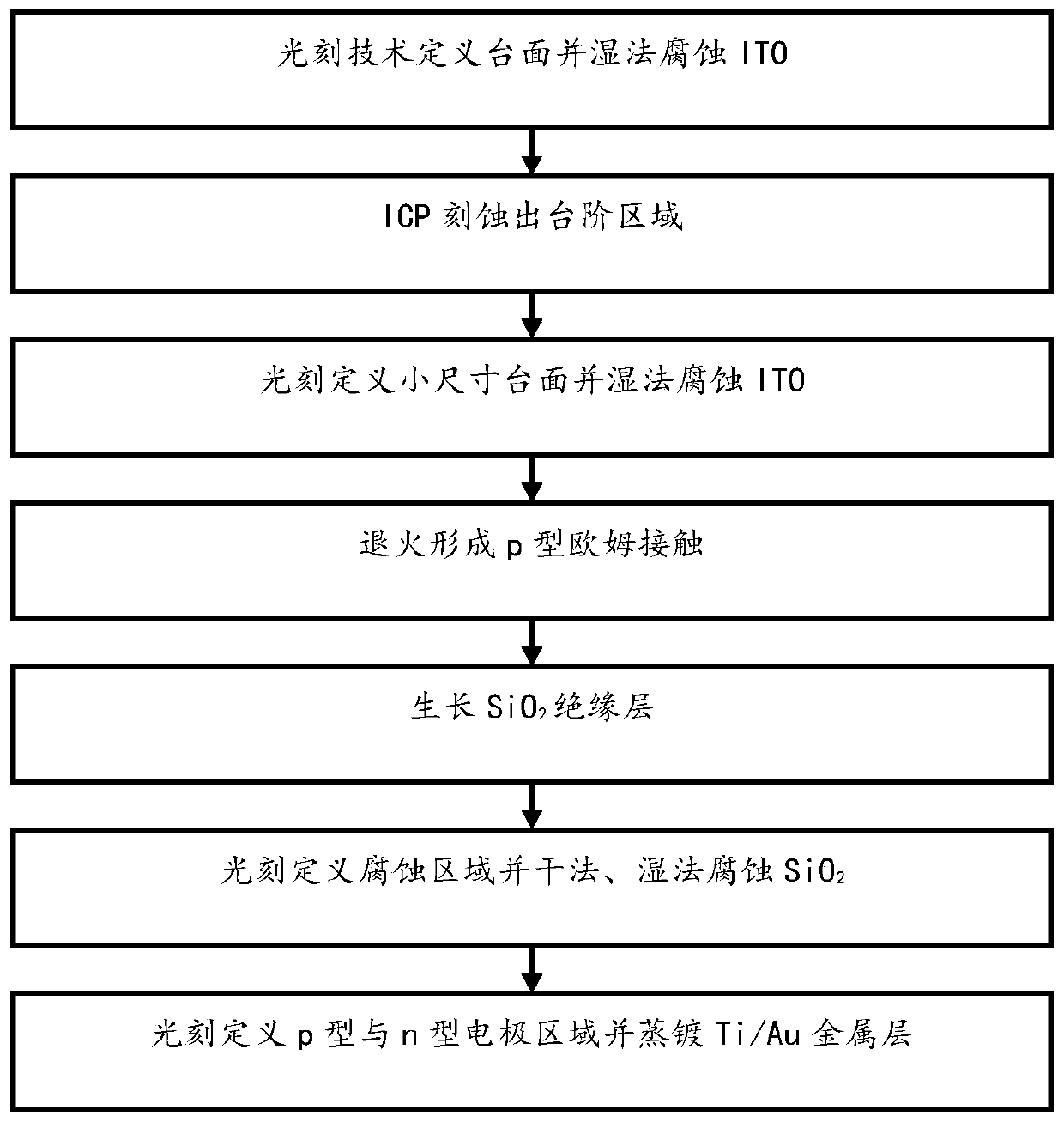

[0045] This embodiment provides a multi-functional micro-LED chip and its preparation method that restricts the carrier transport area by small-sized ITO, such as Figure 3-5 shown.

[0046] Taking the green light epitaxial wafer as an example, it specifically includes the following steps:

[0047] Step 1: From bottom to top, the sapphire substrate includes an unintentionally doped GaN layer of 3 microns, an n-GaN layer of 2 microns, a stress relief layer of 0.3 microns, a multi-quantum well light-emitting layer of 0.17 microns, a p-GaN layer of 0.5 microns, and ITO Electron transport layer; use S1818 photoresist at 4000 rpm, thickness of 1.8 microns to 2.2 microns, use UV photolithography machine (MA6) to expose for 10 seconds, use 0.5% NaOH solution to develop for 50 seconds;

[0048] Step 2: Use concentrated hydrochloric acid / concentrated nitric acid (4:1) mixed solution to corrode for 1 minute and 30 seconds;

[0049] Step 3: Using an Inductively Coupled Plasma Etcher (O...

Embodiment 2

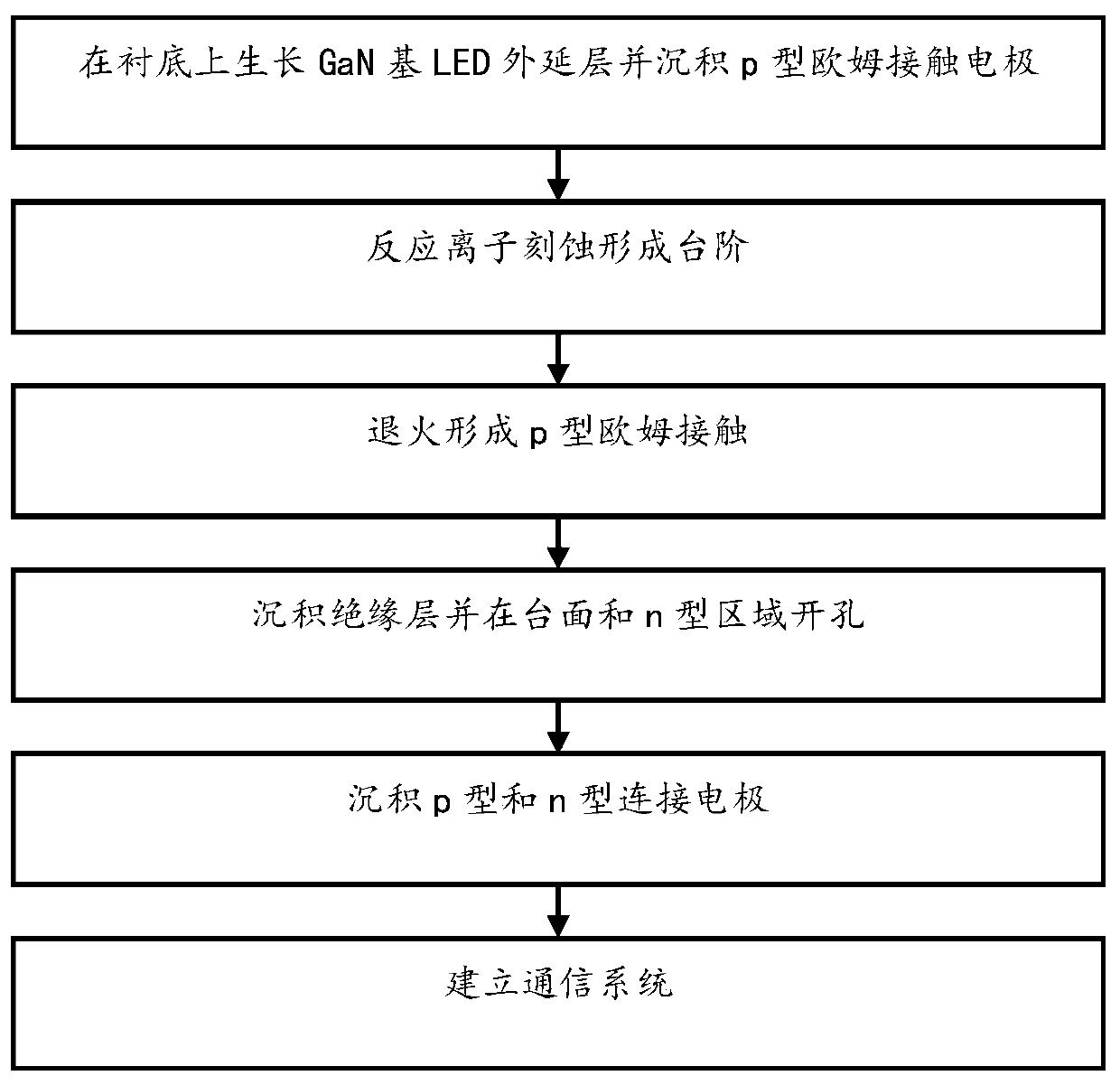

[0076] This embodiment provides a multifunctional micro-LED chip and its preparation method that activates magnesium doping of p-GaN by LEEBI (low-energy electron beam irradiation) to increase the carrier concentration in a limited area to limit the carrier transport area, such as Figure 3-5 shown.

[0077] Step 1: From bottom to top, the sapphire substrate includes an unintentionally doped GaN layer of 3 microns, an n-GaN layer of 2 microns, a stress relief layer of 0.3 microns, a multi-quantum well light-emitting layer of 0.17 microns, and a p-GaN layer of 0.5 microns; using S1818 photoresist at 4000 rpm, with a thickness of 1.8 microns to 2.2 microns, exposed for 10 seconds with a UV lithography machine (MA6), and developed with 0.5% NaOH solution for 50 seconds;

[0078] Step 2: Using an Inductively Coupled Plasma Etcher (Oxford), BCl 3 30sccm, Ar 15sccm, RF power 150 watts, ICP power 1000 watts, air pressure 10 mTorr, temperature 20 degrees Celsius, etching time 6 minu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More